# Formal Modeling of Network-on-Chip and its Applications in Starvation and Deadlock Detection and in Developing Deadlock Free Routing Algorithms

Thesis submitted to the Indian Institute of Technology Guwahati for the award of the degree

# Doctor of Philosophy

in Computer Science and Engineering

> Submitted by Surajit Das

Under the guidance of Dr. Chandan Karfa and Prof. Santosh Biswas

Department of Computer Science and Engineering Indian Institute of Technology Guwahati December, 2021

Copyright © Surajit Das 2021. All Rights Reserved.

Dedicated to my

Aradhya

and

Parents & Wife

and

### All Other Family Members

Who always picked me up on time and encouraged me to go on every adventure, specially this one.

### Declaration

I, Surajit Das, hereby confirm that:

- The work contained in this thesis is original and has been done by myself and under the general supervision of my supervisors.

- The work reported herein has not been submitted to any other Institute for any degree or diploma.

- Whenever I have used materials (concepts, ideas, text, expressions, data, graphs, diagrams, theoretical analysis, results, etc.) from other sources, I have given due credit by citing them in the text of the thesis and giving their details in the references. Elaborate sentences used verbatim from published work have been clearly identified and quoted.

- I also affirm that no part of this thesis can be considered plagiarism to the best of my knowledge and understanding and take complete responsibility if any complaint arises.

Surajit Das Research Scholar Department of SCE IIT Guwahati Guwahati, Assam, India 781039 d.surajit@iitg.ac.in Date: Place:

.....

### Acknowledgements

First and foremost, I would like to express my heartfelt gratitude to my supervisor Dr. Chandan Karfa for his consistent support, inexhaustible patience and positive guidance during my doctoral research. I am thankful for his ethical beliefs and philosophy which made me mature not only as a scientific researcher but also as a human. I am grateful to my second supervisor Prof. Santosh Biswas, who guided me, encourage me in critical phase of my research. I am thankful for his motivation and consistent support during my research.

I am highly grateful to *Prof. Jatindra Kumar Deka* for his invaluable support and encouragement throughout my Ph.D. I would also like to thank the other members of my Doctoral Committee - *Prof. Purandar Bhaduri* and *Dr. John Jose* for their insightful comments and suggestions which made me improve the quality and clarity of my work.

I want to thank the heads of the Department of Computer Science and Engineering during my Ph.D. at IITG - *Prof. Diganta Goswami, Prof. S. V. Rao* and *Prof. Jatindra Kumar Deka* for allowing me to use the facilities and the available resources. I would like to thank Prof. Sukumar Nandi, Prof. Hemangee K. Kapoor, Dr. Aryabartta Sahu, Dr. John Jose and all the other faculty members of Computer Science and Engineering, IITG, from whom I get opportunity to learn during my PhD.

I acknowledge the Technical staff of the Department of Computer Science and Engineering - Mr. Nanu Alan Kachari, Mr. Bhriguraj Borah, Mr. Hemanta Kumar Nath, Mr. Pranjitt Talukdar, Mr. Raktajit Pathak and Mr. Nava Kumar Boro for solving any engineering related issues. I am deeply thankful to - Mr. Monojit Bhattacharjee, Ms. Gauri Khuttiya Deori and Mr. Prabin Bharali for efficiently handling the administrative work. I am obliged to all the the staff and security personnel for their constant help and support. I would also like to thank the staff at the Academic Affairs office who were supportive to process my applications and grant requests.

I would like to gratefully acknowledge *MHRD*, *Govt. of India* for the financial support rendered throughout my years of Ph.D. without which this research could not have taken shape.

I am indeed thankful to my fellow lab mates Ramanuj, Debabrata, Priyanka, Mohammad, Nilotpala, Alakesh, Ujjwal, Dipojwal, Swarup, Chitra, Pawan, Arijit, Palash, Parikshit, Partha, Pallabi, Nayantara, Dipika, Deepak, Sukarn, Saptarchi, Balaprakash, Manoj, Hemakumar and many more for creating a wonderful experience during my PhD. It was a good experience to work with Ajinka and Pavan for a few months and I like to thank them for being part of my PhD journey. I would like to thank my senior lab mates Dr. Shirshendu Das for his support and helping me in PARSEC benchmark. I would like to thank other senior lab mates Dr. Shounak Chakraborty , Dr. Mayank Agarwal, Dr. Pradeep Kumar Biswal, Dr. Shilpa Budhkar, Dr. Nilakanta Sahu, Dr. Manojit Gosh for their guidance. I would also like to thank all the research scholars of the department of Computer Science and Engineering at IITG for creating a warm atmosphere of mutual support and encouragement. The stimulating discussions, brainstorming and sleepless night working together contribute a significant portion towards my development as an independent researcher.

I want to thank the friends from my school days - Biswajit, Dipankar, Mukul, Pankaj, Rupam, Pulin, Pranab and many more for the beautiful memories and their encouragement for PhD. Finally yet importantly, I would like to thank Lord Krishna and my family - Maa, Deuta, Aradhya, Junuk, Dishant, Kakali, Dada, Baideu, Bau, Vindeu, Mama, Mami and Partha for their unconditional love, support, caring, warmth and profound encouragement all these years. They never doubted my intentions and whole-heartedly supported me in all my endeavours. I fall short of words to express my gratitude to them.

> Surajit Das Research Scholar Department of SCE IIT Guwahati Guwahati, Assam, India 781039 d.surajit@iitg.ac.in

Department of Computer Science and Engineering Indian Institute of Technology Guwahati Guwahati - 781039, Assam, India

This is to certify that this thesis entitled, "Formal Modeling of Network-on-Chip and its Applications in Starvation and Deadlock Detection and in Developing Deadlock Free Routing Algorithms", being submitted by Mr. Surajit Das, to the Department of Computer Science and Engineering, Indian Institute of Technology Guwahati, for partial fulfillment of the award of the degree of Doctor of Philosophy, is a bonafide work carried out by him under my supervision and guidance. The thesis, in my opinion, is worthy of consideration for award of the degree of Doctor of Philosophy in accordance with the regulation of the institute.

To the best of my knowledge, this thesis has not been submitted in part or full to any other university or institute for the award of any degree or diploma.

#### Dr. Chandan Karfa

Associate Professor Department of Computer Science and Engineering IIT Guwahati Date: Place:

#### .....

**Prof. Santosh Biswas** Professor Department of Electrical Engineering and Computer Science IIT Bhilai Date: Place:

### Abstract

The increasing demand for high computation speed in devices ranging from a handheld smartphone to a time critical missile defense system along with the issue of heat generated by a high frequency processor motivates the researchers to explore Chip Multi-Processors (CMP) architecture. In CMP, multiple processors with moderate clock frequencies are integrated into single chip. For facilitating a fast and efficient communicating infrastructure between processors, a programmable network having routers connected to each processor is used in CMPs which is formally known as Network-on-Chip (NoC). A routing algorithm in NoC helps in directing packets efficiently between processors via routers. While routing packets, situations like starvation or deadlock may occur that degrade the performance of NoC. Formal modeling of NoC is helpful to detect such scenarios either by using a model checker or by developing a simulation framework on the formal model.

In this thesis, formal modeling of NoC using Finite State Machines (FSMs) is presented first. NoC components like a buffer for the temporary storage of packets, switch for directing packets towards proper output ports and arbiter for resolving conflict at an output port are modeled using FSMs. Two arbitration logic, namely fixed-priority arbiter and roundrobin arbiter, are modeled as FSMs. The synchronization between NoC components is maintained using dedicated FSMs. The correctness of the FSM based NoC model is checked and verification of starvation freedom is also presented using model checker in this work. Since modeling synchronization amongst components in an NoC is a complex task in FSM model and model checking based verification of global properties like deadlock is not feasible due to large state space, we next model the NoC using Communicating Finite State Machines (CFSMs). In CFSM based NoC model, the synchronization between NoC components is maintained with the help of message passing. No special state machine for maintaining system wide synchronization is required. We have automated the CFSM based NoC model generation process for Mesh and Torus NoCs. A CFSM based formal simulation framework is then developed for application specific deadlock detection in NoC. The CFSM based simulation framework detects confirmed deadlock conditions in given traffic with respect to a given routing algorithm and given topology. On detecting a confirmed deadlock, the framework reports the deadlock with the instance of cyclic resource dependencies.

The instance of cyclic resource dependency obtained as an output from the CFSM based framework helps in formulating deadlock avoidance. Representation of deadlock in a formal and informative way helps in understanding the root cause of deadlock and in turn helps in avoiding them. The Turn model [1] and Channel Dependency Graph (CDG) [2] are two classical approaches used for theoretical deadlock detection and representation of deadlock scenarios. We have proposed Directional Dependency Graph (DDG) for representing deadlock cycles in an informative way by incorporating Turn, wraparound channel and direction information with CDG in a simplified form. The DDG is helpful in showing deadlock scenarios or deadlock freedom for a routing procedure. It is found that Torus NoC is more deadlock prone in comparison to Mesh NoC due to the presence of ring networks with inherent cyclic paths. Virtual Channels (VCs) or additional buffers are mostly used for avoiding deadlock in Torus NoC. Therefore, an Arc model is proposed for avoiding deadlock in Torus NoC without using additional resources like VC or additional buffer. Deadlock behaviour of the proposed Arc model with respect to XY-Turns is also presented. An approach of developing deadlock free routing algorithms using a subset of Arcs and a given set of Turns is also presented. Finally, the utility of the Arc Model and DDG are presented by demonstrating the deadlock free algorithms for Torus NoC. Our proposed Arc based routing algorithms in Torus NoC.

Keywords- Network-on-Chip, Formal Verification, Starvation, Deadlock Detection, Deadlock Avoidance, Finite State Machine, Communicating Finite State Machine

๛๛**๛ฺ**๛๛

### Contents

| 1 | Intr                | Introduction 1 |                                                                    |    |

|---|---------------------|----------------|--------------------------------------------------------------------|----|

|   | 1.1 Network-on-Chip |                | 2                                                                  |    |

|   |                     | 1.1.1          | Correct Functioning of NoC                                         | 4  |

|   |                     | 1.1.2          | Verification of NoC                                                | 5  |

|   | 1.2                 | Challe         | enges in Formal Modeling and Verification of NoC                   | 6  |

|   |                     | 1.2.1          | Starvation Freedom in NoC                                          | 6  |

|   |                     | 1.2.2          | Deadlock Detection in NoC                                          | 6  |

|   |                     |                | 1.2.2.1 Application Specific Deadlock Detection                    | 7  |

|   |                     | 1.2.3          | Deadlock Representation and its Avoidance                          | 9  |

|   |                     |                | 1.2.3.1 Channel Dependency Graph                                   | 9  |

|   |                     |                | 1.2.3.2 Turn Model                                                 | 10 |

|   |                     |                | 1.2.3.3 Deadlock in Torus NoC and its Avoidance                    | 11 |

|   |                     | 1.2.4          | Formal Modeling of NoC                                             | 12 |

|   | 1.3                 | Thesis         | s Objectives                                                       | 13 |

|   | 1.4                 | Contri         | ibutions of the Thesis                                             | 15 |

|   |                     | 1.4.1          | Formal Modeling of NoC using FSM and Verification of Starvation    |    |

|   |                     |                | using Model Checker                                                | 15 |

|   |                     | 1.4.2          | Formal Modeling of NoC using CFSM and Developing a Simulation      |    |

|   |                     |                | Framework for Deadlock Detection                                   | 17 |

|   |                     | 1.4.3          | Deadlock Avoidance in Torus NoC using Arc Model and DDG $\ldots$ . | 18 |

|   |                     | 1.4.4          | Deadlock Free Routing Algorithms for Torus NoC using Arc Model .   | 19 |

|   | 1.5                 | Organ          | ization of the Thesis                                              | 20 |

| 2 | Bac                 | kgrou          | nd and Literature Survey                                           | 23 |

|   | 2.1                 | Forma          | l Verification Techniques                                          | 24 |

|   |                     | 2.1.1          | Model Checking                                                     | 24 |

|   |                     | 2.1.2          | Equivalent Checking                                                | 26 |

|   |                     | 2.1.3          | Theorem Prover                                                     | 26 |

|   | 2.2                 | Forma          | Al Modeling and Verification of NoC                                | 26 |

|   |            | 2.2.1                                                                                                     | Formal Modeling using Different Formalism                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                                                                             |

|---|------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | 2.2.2                                                                                                     | Formal Modeling using xMAS Primitives                                                                                                                                                                                                                                                                                                                                                                                                              | 30                                                                                                                                             |

|   |            | 2.2.3                                                                                                     | Modeling using FSM and CFSM                                                                                                                                                                                                                                                                                                                                                                                                                        | 31                                                                                                                                             |

|   |            | 2.2.4                                                                                                     | Traffic Modeling using Queuing Approach                                                                                                                                                                                                                                                                                                                                                                                                            | 32                                                                                                                                             |

|   |            | 2.2.5                                                                                                     | Run-time Deadlock Detection                                                                                                                                                                                                                                                                                                                                                                                                                        | 33                                                                                                                                             |

|   |            | 2.2.6                                                                                                     | Challenges and Objective                                                                                                                                                                                                                                                                                                                                                                                                                           | 33                                                                                                                                             |

|   | 2.3        | Routin                                                                                                    | ng Algorithms for NoC                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                                                                                                                             |

|   | 2.4        | Deadle                                                                                                    | ock Avoidance in a Routing Algorithm                                                                                                                                                                                                                                                                                                                                                                                                               | 36                                                                                                                                             |

|   |            | 2.4.1                                                                                                     | Up*/Down* and Turn Model Approach                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                                                             |

|   |            | 2.4.2                                                                                                     | FirstHop Routing for Avoiding Deadlock in Torus NoC                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                                                                                             |

|   |            | 2.4.3                                                                                                     | Dally's Approach with Virtual Channel                                                                                                                                                                                                                                                                                                                                                                                                              | 38                                                                                                                                             |

|   |            | 2.4.4                                                                                                     | Duato's Approach with Escape Path and Virtual Channel                                                                                                                                                                                                                                                                                                                                                                                              | 38                                                                                                                                             |

|   |            | 2.4.5                                                                                                     | Bubble Flow Control with Dedicated Buffer                                                                                                                                                                                                                                                                                                                                                                                                          | 39                                                                                                                                             |

|   |            | 2.4.6                                                                                                     | Other Approaches                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39                                                                                                                                             |

|   |            | 2.4.7                                                                                                     | Challenges and Objectives                                                                                                                                                                                                                                                                                                                                                                                                                          | 40                                                                                                                                             |

|   | 2.5        | Conclu                                                                                                    | isions                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40                                                                                                                                             |

| 3 | For        | mal M                                                                                                     | adding of NoC using FSM and Varifaction of Stamption using                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                |

| 3 |            | del Ch                                                                                                    | odeling of NoC using FSM and Verification of Starvation using                                                                                                                                                                                                                                                                                                                                                                                      | 43                                                                                                                                             |

|   | 3.1        |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>43</b>                                                                                                                                      |

|   | 0.1        | 3.1.1                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44                                                                                                                                             |

|   |            | 3.1.2                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                |

|   | 2.0        |                                                                                                           | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45                                                                                                                                             |

|   | 32         |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45<br>46                                                                                                                                       |

|   | 3.2        | Finite                                                                                                    | State Machine and the Naming Convention                                                                                                                                                                                                                                                                                                                                                                                                            | 46                                                                                                                                             |

|   | 3.2        | Finite<br>3.2.1                                                                                           | State Machine and the Naming Convention                                                                                                                                                                                                                                                                                                                                                                                                            | 46<br>46                                                                                                                                       |

|   |            | Finite<br>3.2.1<br>3.2.2                                                                                  | State Machine and the Naming Convention          Finite State Machine          Short forms and the Naming Convention                                                                                                                                                                                                                                                                                                                               | 46<br>46<br>47                                                                                                                                 |

|   | 3.2<br>3.3 | Finite<br>3.2.1<br>3.2.2<br>Forma                                                                         | State Machine and the Naming Convention          Finite State Machine          Short forms and the Naming Convention          I Modeling of NoC using FSM                                                                                                                                                                                                                                                                                          | 46<br>46<br>47<br>48                                                                                                                           |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1                                                                | State Machine and the Naming Convention                                                                                                                                                                                                                                                                                                                                                                                                            | 46<br>46<br>47<br>48<br>49                                                                                                                     |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma                                                                         | State Machine and the Naming Convention                                                                                                                                                                                                                                                                                                                                                                                                            | 46<br>46<br>47<br>48<br>49<br>50                                                                                                               |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1                                                                | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionI Modeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers                                                                                                                                                                                          | 46<br>47<br>48<br>49<br>50<br>50                                                                                                               |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1<br>3.3.2                                                       | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionShort forms and the Naming ConventionModeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers3.3.2.2Synchronization within Router Components                                                                                                        | 46<br>46<br>47<br>48<br>49<br>50<br>50<br>50                                                                                                   |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1                                                                | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionShort forms and the Naming ConventionModeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers3.3.2.2Synchronization within Router ComponentsModeling Buffer using FSM                                                                               | <ul> <li>46</li> <li>46</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> </ul>                         |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1<br>3.3.2                                                       | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionI Modeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers3.3.2.2Synchronization within Router ComponentsModeling Buffer using FSM3.3.3.1FSM model of Sync                                                                                          | <ul> <li>46</li> <li>46</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>51</li> </ul>             |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1<br>3.3.2<br>3.3.3                                              | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionI Modeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers3.3.2.2Synchronization within Router ComponentsModeling Buffer using FSM3.3.3.1FSM model of Sync3.3.2FSM model of Buffer                                                                  | <ul> <li>46</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>53</li> </ul>                         |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.3                                     | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionI Modeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers3.3.2.2Synchronization within Router ComponentsModeling Buffer using FSM3.3.1FSM model of Sync3.3.2FSM model of BufferFSM Model of Switch                                                 | <ul> <li>46</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>51</li> <li>51</li> <li>53</li> <li>53</li> </ul>             |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.3                                     | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionI Modeling of NoC using FSMI Modeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers3.3.2.2Synchronization within Router ComponentsModeling Buffer using FSM3.3.3.1FSM model of Sync3.3.2FSM model of BufferFSM Model of SwitchFSM Model of Return | <ul> <li>46</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>53</li> <li>53</li> <li>55</li> </ul> |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6 | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionI Modeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers3.3.2.2Synchronization within Router ComponentsModeling Buffer using FSM3.3.3.1FSM model of Sync3.3.2.7FSM model of BufferFSM Model of ReturnApproach for Designing Virtual Channels      | <ul> <li>46</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>51</li> <li>51</li> <li>53</li> <li>55</li> <li>56</li> </ul> |

|   |            | Finite<br>3.2.1<br>3.2.2<br>Forma<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.3                                     | State Machine and the Naming ConventionFinite State MachineShort forms and the Naming ConventionI Modeling of NoC using FSMI Modeling of NoC using FSMHigh-Level Overview of the Movement of PacketsSynchronization between NoC Components3.3.2.1Synchronization between two Routers3.3.2.2Synchronization within Router ComponentsModeling Buffer using FSM3.3.3.1FSM model of Sync3.3.2FSM model of BufferFSM Model of SwitchFSM Model of Return | <ul> <li>46</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>53</li> <li>53</li> <li>55</li> </ul> |

|   |                   |                              | 3.3.7.2 FSM Model of Round-robin Arbiter                                           | 58       |

|---|-------------------|------------------------------|------------------------------------------------------------------------------------|----------|

|   | 3.4               | 3.4 Correctness of the Model |                                                                                    |          |

|   |                   | 3.4.1                        | Progress in Router Components                                                      | 61       |

|   |                   |                              | 3.4.1.1 Progress in a Buffer                                                       | 62       |

|   |                   |                              | 3.4.1.2 Progress in a Switch                                                       | 62       |

|   |                   |                              | 3.4.1.3 Progress in a Fixed-priority and Round-robin Arbiters                      | 62       |

|   |                   | 3.4.2                        | Synchronization within a Router                                                    | 63       |

|   |                   | 3.4.3                        | Correctness of a Priority Generator                                                | 64       |

|   | 3.5               | Applic                       | eation of the Model                                                                | 64       |

|   |                   | 3.5.1                        | Verification of Starvation-freedom                                                 | 65       |

|   |                   | 3.5.2                        | Verification of Transfer of Packets                                                | 66       |

|   |                   | 3.5.3                        | Verification of Overall NoC                                                        | 66       |

|   |                   |                              | 3.5.3.1 Number of FSMs in an NoC                                                   | 66       |

|   |                   |                              | 3.5.3.2 Active Windows                                                             | 68       |

|   | 3.6               | Exper                        | imental Results and Analysis                                                       | 69       |

|   |                   | 3.6.1                        | Verification of Progress, Synchronization and Priority Generation within           |          |

|   |                   |                              | a Router                                                                           | 69       |

|   |                   |                              | 3.6.1.1 Runtime Improvement with Parallel Execution considering                    |          |

|   |                   |                              | Individual Router                                                                  | 70       |

|   |                   | 3.6.2                        | Verification of Transfer of Packets and Starvation Freedom considering             |          |

|   |                   |                              | Active Windows                                                                     | 71       |

|   |                   |                              | 3.6.2.1 Analysis of the Findings on Starvation Freedom                             | 72       |

|   |                   |                              | 3.6.2.2 Runtime Improvement with Parallel Execution for the Ac-                    |          |

|   |                   |                              | tive Windows                                                                       | 73       |

|   | 3.7               | Conclu                       | usion                                                                              | 74       |

|   | Ð                 | 1 7 4                        |                                                                                    |          |

| 4 |                   |                              | odeling of NoC using CFSM and Developing a Simulation Frame-<br>Deadlock Detection | 77       |

|   | <b>wor</b><br>4.1 |                              |                                                                                    | 77       |

|   | 4.1<br>4.2        |                              | uction                                                                             | 78       |

|   | 4.2               | 4.2.1                        | Formal Modeling of NoCs using CFSM                                                 | 78       |

|   |                   |                              | 0 0                                                                                |          |

|   | 4.3               | 4.2.2                        | Development of CFSM based Simulation Framework                                     | 79<br>81 |

|   | 4.3<br>4.4        |                              | round of Communicating Finite State Machine based Modeling                         | 81<br>84 |

|   | 4.4               | Forma<br>4.4.1               | I Modeling of NoC using CFSM                                                       | 84<br>85 |

|   |                   | 4.4.1<br>4.4.2               | Naming Convention                                                                  | 85<br>85 |

|   |                   | 4.4.2                        | Modeling Buffer                                                                    |          |

|   |                   |                              | 4.4.2.1 Buffer with single slot                                                    | 87<br>87 |

|   |                   |                              | 4.4.2.2 Buffer with more than one slots                                            | 87       |

|   |     | 4.4.3  | Modeling Switch and Route Computation                                  | 89  |

|---|-----|--------|------------------------------------------------------------------------|-----|

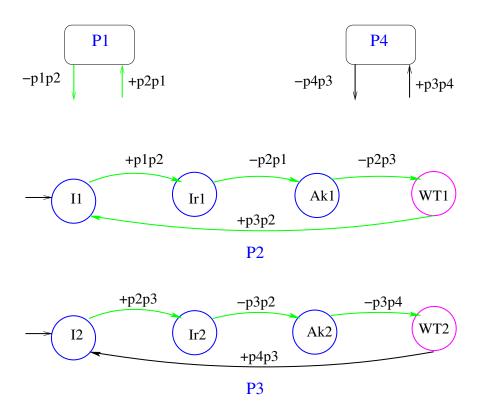

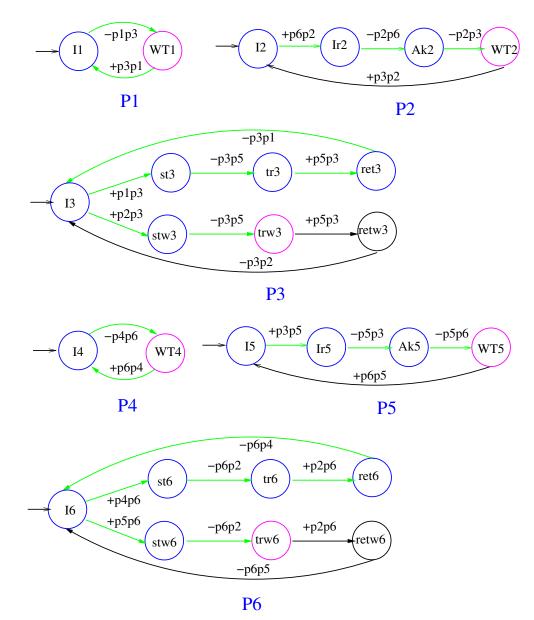

|   |     | 4.4.4  | Modeling Arbiter and Scheduler                                         | 91  |

|   |     |        | 4.4.4.1 Changing of priority in round-robin fashion                    | 91  |

|   |     |        | 4.4.4.2 Transmitting the packet from current router to the next router | 93  |

|   |     | 4.4.5  | Modeling Virtual Channel                                               | 93  |

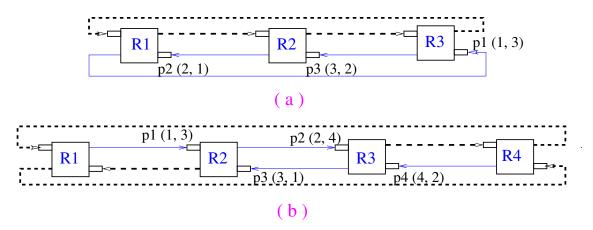

|   | 4.5 | Propo  | sed Scheme for Deadlock Detection                                      | 95  |

|   |     | 4.5.1  | Delayed Reception                                                      | 95  |

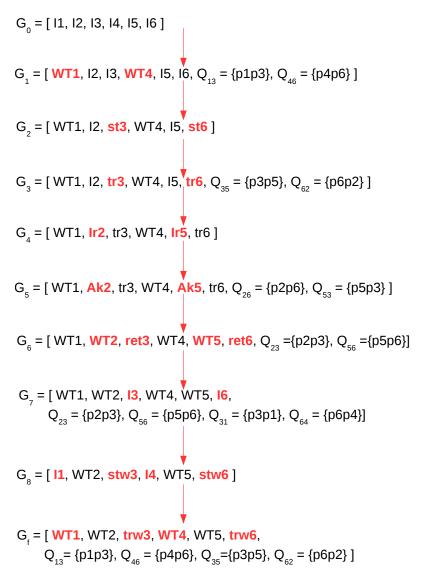

|   |     | 4.5.2  | Representation of Deadlock in NoC using CFSM                           | 97  |

|   |     | 4.5.3  | Deadlock Detection Framework                                           | 102 |

|   | 4.6 | Auton  | nation of CFSM Model Generation                                        | 103 |

|   |     | 4.6.1  | Bounded Communication                                                  | 105 |

|   |     | 4.6.2  | Complexity of the CFSM Model                                           | 106 |

|   | 4.7 | Exper  | imental Results and Analysis                                           | 107 |

|   |     | 4.7.1  | Experiment I: XY-routing on Mesh and Torus of Different Sizes          | 108 |

|   |     | 4.7.2  | Experiment II: XY-routing on Mesh and Torus with Different Traffic     |     |

|   |     |        | Size                                                                   | 110 |

|   |     | 4.7.3  | Experiment III: Deadlock Detection on Dynamic XY-routing and Mod-      |     |

|   |     |        | ified West-First routing                                               | 111 |

|   |     | 4.7.4  | Experiment IV: Deadlock Avoidance with Increasing Buffer Size          | 113 |

|   |     | 4.7.5  | Experiment V: Detection of False Positive Deadlock Warning in Book-    |     |

|   |     |        | sim Simulator                                                          | 115 |

|   |     | 4.7.6  | Justification for Deadlock in Adaptive Routing Algorithms              | 115 |

|   | 4.8 | Conch  | usion                                                                  | 116 |

| 5 | Dea | dlock  | Avoidance in Torus NoC Using Arc Model and DDG 1                       | 19  |

|   | 5.1 | Introd | luction                                                                | 119 |

|   |     | 5.1.1  | Cyclic Resource Dependency in Torus NoC                                | 120 |

|   |     | 5.1.2  | Deadlock and its Representation in NoC                                 | 122 |

|   |     |        | 5.1.2.1 Channel Dependency Graph                                       | 122 |

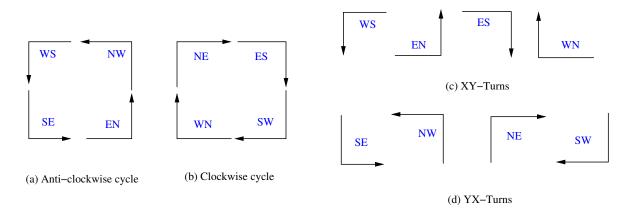

|   |     |        | 5.1.2.2 Turn Model                                                     | 123 |

|   |     | 5.1.3  | Does Deadlock Always Possible in Torus due to Wraparound Channel?      | 124 |

|   | 5.2 | Motiv  | ation and Contribution                                                 | 125 |

|   |     | 5.2.1  | Deadlock Representation in Torus NoC                                   | 126 |

|   |     | 5.2.2  | Deadlock Avoidance in Torus NoC                                        | 126 |

|   |     | 5.2.3  | Contributions                                                          | 127 |

|   | 5.3 | The A  | rc Model for Avoiding Deadlock in Torus                                | 128 |

|   |     | 5.3.1  | Restricted Move via Wraparound Channel                                 | 128 |

|   |     | 5.3.2  | Classification of Wraparound Channels                                  | 129 |

|                                        |     | 5.3.3                                                                 | The Proposed Arc Model                                                                             |

|----------------------------------------|-----|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                        |     | 5.3.4 Effect of Arcs with the Permitted Turns in the Mesh Sub-network |                                                                                                    |

| 5.4 Directional Dependency Graph       |     | ional Dependency Graph                                                |                                                                                                    |

| 5.4.1 Application of Arc Model and DDG |     | Application of Arc Model and DDG                                      |                                                                                                    |

|                                        | 5.5 | Case                                                                  | Study: Arcs with XY-Turns                                                                          |

| 5.5.1 Single Arc with XY-Turns         |     | 5.5.1                                                                 | Single Arc with XY-Turns                                                                           |

|                                        |     |                                                                       | 5.5.1.1 Turns Introduced due to Arcs $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 136$ |

|                                        |     |                                                                       | 5.5.1.2 Deadlock Freedom for Individual Arc                                                        |

|                                        |     | 5.5.2                                                                 | Deadlock Detection for Arc Pairs with XY-Turns                                                     |

|                                        |     |                                                                       | 5.5.2.1 Deadlock in Arc Pairs from the same Wraparound Channel . 138                               |

|                                        |     |                                                                       | 5.5.2.2 Deadlock due to Added Turns by Arcs                                                        |

|                                        |     |                                                                       | 5.5.2.3 Deadlock with a Combination of X-Arc and Y-Arc 141                                         |

|                                        |     | 5.5.3                                                                 | Deadlock Avoidance using DDG Representation                                                        |

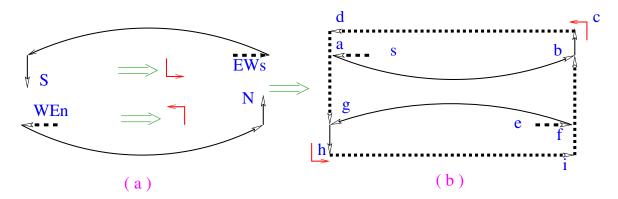

|                                        |     |                                                                       | 5.5.3.1 Deadlock avoidance for $(EWs + WEn)$ Arcs with XY-Turns 143                                |

|                                        |     |                                                                       | 5.5.3.2 Deadlock avoidance for $(NSw + EWn)$ Arcs with XY-Turns 143                                |

|                                        |     | 5.5.4                                                                 | Checking Deadlock Freedom using DDG                                                                |

|                                        | 5.6 | Experi                                                                | imental Deadlock Detection                                                                         |

|                                        |     | 5.6.1                                                                 | Experimental Results for Arc Pairs with XY-Turns                                                   |

|                                        |     | 5.6.2                                                                 | Deadlock Scenarios generated by CFSM Framework                                                     |

|                                        |     |                                                                       | 5.6.2.1 Deadlock Scenarios for (EWs + EWn) Arc with XY-Turn $\therefore$ 147                       |

|                                        |     |                                                                       | 5.6.2.2 Deadlock Scenarios for $(EWs + WEn)$ Arc with XY-Turn . 149                                |

|                                        |     |                                                                       | 5.6.2.3 Deadlock Scenarios for $(EWn + NSw)$ Arc with XY-Turn . 150                                |

|                                        | 5.7 | Conclu                                                                | usion                                                                                              |

| 6                                      | Dee | dloale                                                                | Free Routing Algorithms for Torus NoC using Arc Model 151                                          |

| U                                      | 6.1 |                                                                       | uction                                                                                             |

|                                        | 0.1 | 6.1.1                                                                 | Contributions         151                                                                          |

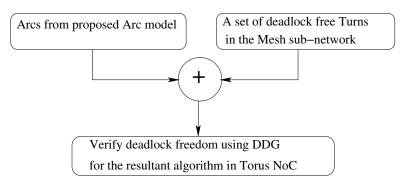

|                                        | 6.2 |                                                                       | ock Free Routing Algorithm Design Approach using Arc Model 155                                     |

|                                        | 6.3 |                                                                       | ng using Two Arcs along with XY-Turns                                                              |

|                                        | 0.0 | 6.3.1                                                                 | Routing steps for Algorithm 1    1                                                                 |

|                                        |     | 6.3.2                                                                 | Deadlock freedom for Algorithm 1                                                                   |

|                                        | 6.4 |                                                                       | num Possible Arcs with XY-Turns in a Routing Algorithm 160                                         |

|                                        | 0.1 | 6.4.1                                                                 | Evaluation plan    100                                                                             |

|                                        |     | 6.4.2                                                                 | Considering deadlock free Arc pairs in X-direction                                                 |

|                                        |     | 6.4.3                                                                 | Considering deadlock free Arc pairs in Y-direction                                                 |

|                                        | 6.5 |                                                                       | ng using Three Arcs with XY-Turns                                                                  |

|                                        | 0.0 | 6.5.1                                                                 | Routing steps for Algorithm 2    162                                                               |

|                                        |     | 6.5.2                                                                 | Deadlock Freedom for Algorithm 2                                                                   |

|                                        |     | 0.0.2                                                                 |                                                                                                    |

|    | 6.6  | Comb    | ination of Arc Model and FirstHop Method                              | 165   |

|----|------|---------|-----------------------------------------------------------------------|-------|

|    |      | 6.6.1   | DDG for Wraparound Channel with FirstHop Restriction                  | 166   |

|    |      | 6.6.2   | Routing using Algorithm 2 and Wraparound Channel with FirstHop        |       |

|    |      |         | Restriction                                                           | 166   |

|    |      |         | 6.6.2.1 Wrap<br>around Channel Compatible with Algorithm 2 $\ldots$   | 167   |

|    |      |         | 6.6.2.2 Routing steps for Algorithm 3                                 | 168   |

|    |      |         | 6.6.2.3 DDG to show Deadlock Freedom for Algorithm 3                  | 171   |

|    | 6.7  | Exper   | imental Results                                                       | 172   |

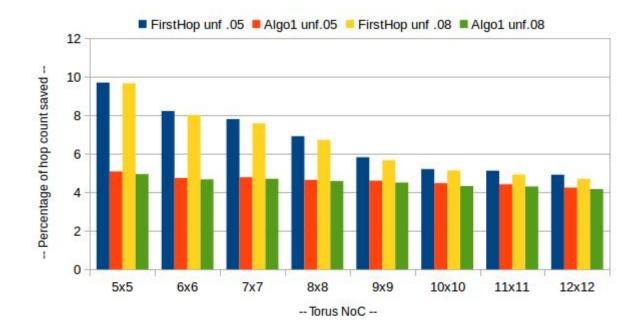

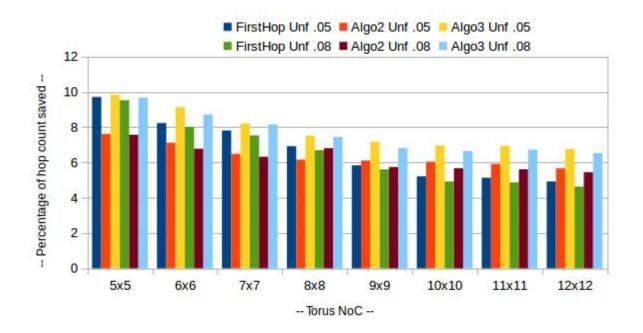

|    |      | 6.7.1   | Comparing FirstHop Algorithm with the Algorithm 1                     | 173   |

|    |      |         | 6.7.1.1 Effects of the Percentage of Traffic Injected from the Bound- |       |

|    |      |         | ary Routers                                                           | 174   |

|    |      | 6.7.2   | Comparisons of Algorithm 2 with Algorithm 1, Up*/Down* Algo-          |       |

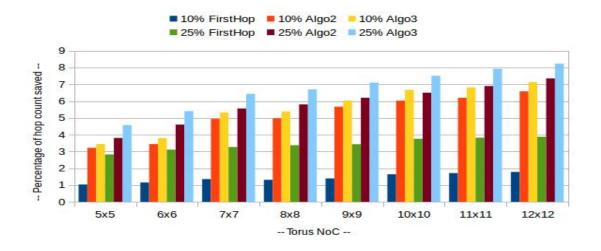

|    |      |         | rithm and FirstHop Algorithm                                          | 176   |

|    |      | 6.7.3   | Comparison for the Algorithm 3 with Algorithm 2 and FirstHop Al-      |       |

|    |      |         | gorithm                                                               | 178   |

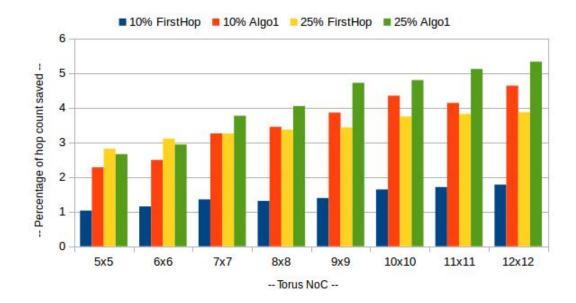

|    |      |         | 6.7.3.1 Effects of the Percentage of Traffic Injected from the Bound- |       |

|    |      |         | ary Routers                                                           | 178   |

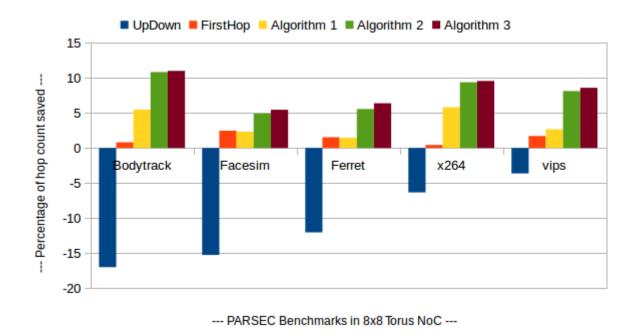

|    |      | 6.7.4   | Hop Count Savings for PARSEC Benchmark Suites                         | 179   |

|    | 6.8  | Concl   | usions                                                                | 180   |

| 7  | Cor  | nclusio | ns and Future Perspectives                                            | 183   |

|    | 7.1  | Summ    | ary of Contributions                                                  | 183   |

|    |      | 7.1.1   | FSM based NoC Model for Verification of Starvation                    | 183   |

|    |      | 7.1.2   | Application Specific Deadlock Detection using CFSM based NoC Mode     | el184 |

|    |      | 7.1.3   | Deadlock Representation and Avoidance Approach in Torus NoC $$        | 185   |

|    |      | 7.1.4   | Deadlock Free Routing Algorithms for Torus NoC                        | 185   |

|    | 7.2  | Future  | e Directions                                                          | 186   |

|    | 7.3  | Concl   | usions                                                                | 187   |

| Pu | blic | ations  |                                                                       | 189   |

| Re | fere | nces    |                                                                       | 190   |

# List of Figures

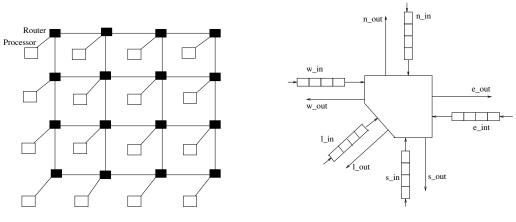

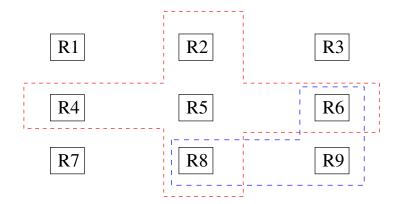

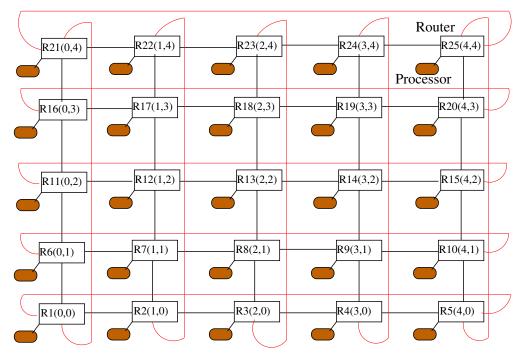

| 1.1  | A 4x4 Mesh NoC                                                               | 2  |

|------|------------------------------------------------------------------------------|----|

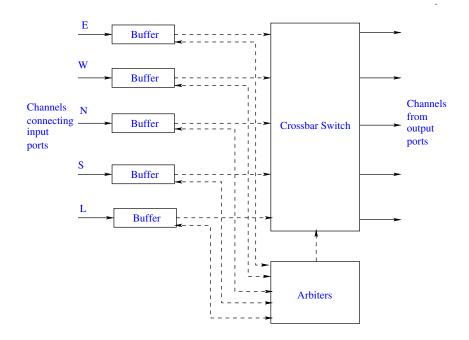

| 1.2  | 5 Port NoC router                                                            | 2  |

| 1.3  | Simplified block diagram depicting functional units in an NoC router [3]     | 3  |

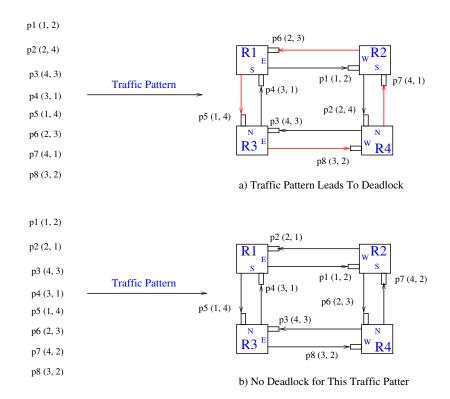

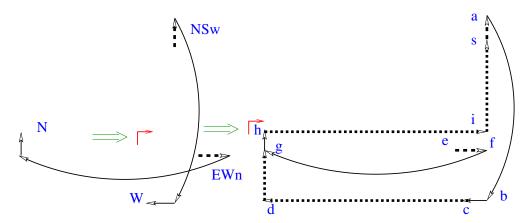

| 1.4  | Deadlock example: (a) Traffic patterns leads to deadlock, (b) No deadlock in |    |

|      | another traffic pattern.                                                     | 8  |

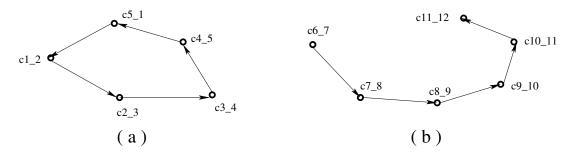

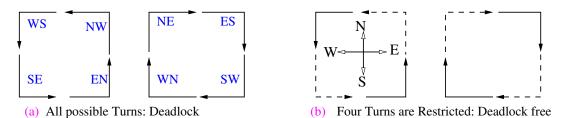

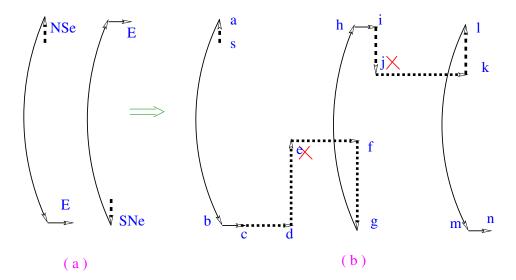

| 1.5  | Channel Dependency Graph: (a) Deadlock cycle, (b) No deadlock $\hdots$       | 9  |

| 1.6  | Turn model: (a) All possible Turns create deadlock, (b) XY-Turns (solid      |    |

|      | lines) and YX-Turns (dotted lines) are deadlock free                         | 10 |

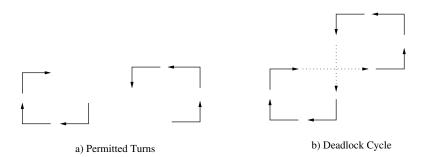

| 1.7  | Deadlock cycle from Turn model: (a) Permitted Turns by a routing algorithm,  |    |

|      | (b) Deadlock cycle                                                           | 10 |

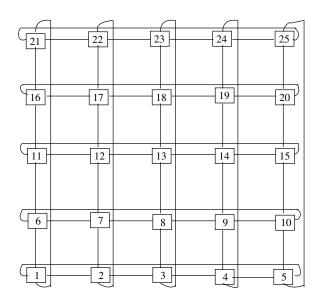

| 1.8  | A 5x5 Torus NoC composed of ring networks                                    | 11 |

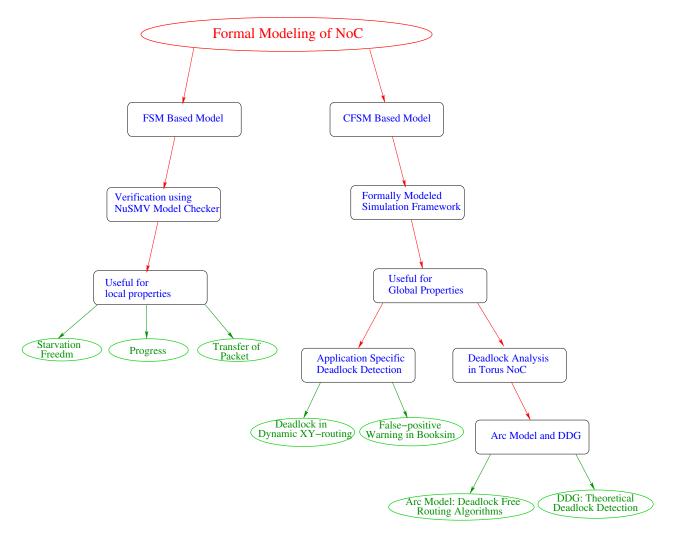

| 1.9  | A high-level overview of the contributions from the thesis                   | 16 |

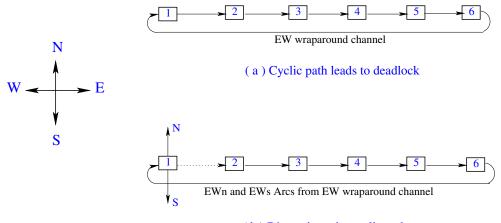

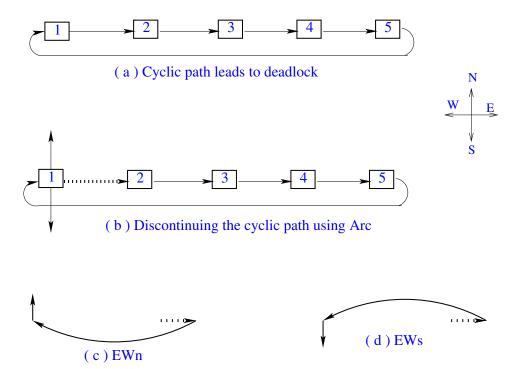

| 1.10 | Avoid deadlock by discontinuing the cyclic path                              | 18 |

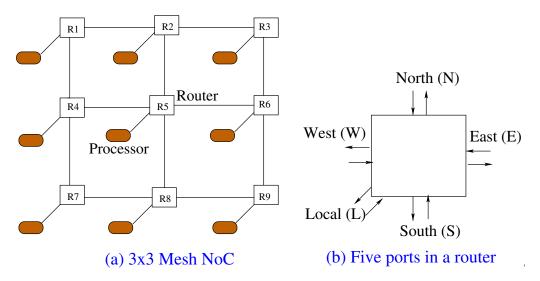

| 3.1  | A 3x3 Mesh NoC and five bidirectional ports in a router                      | 44 |

| 3.2  | Movement of packets from router R5 to R2, and synchronization using Return   |    |

|      | and Sync FSMs                                                                | 49 |

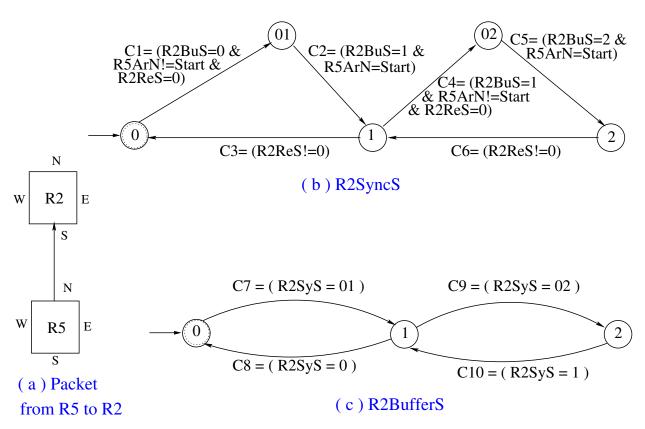

| 3.3  | Buffer and sync: (a) Packets from R5 to R2, (b) R2SyncS: Synchronizing       |    |

|      | between R2BufferS and R5ArbiterN, (c) R2BufferS: Buffer at S input port of   |    |

|      | R2                                                                           | 52 |

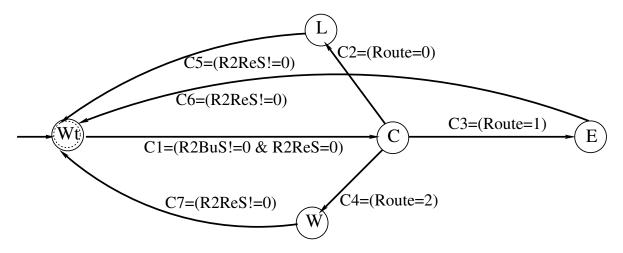

| 3.4  | R2SwitchS: Switch at South Port of R2                                        | 54 |

| 3.5  | R2ReturnS: Synchronization between S port Buffer, S port Switch and Ar-      |    |

|      | biters at L, E and W ports                                                   | 55 |

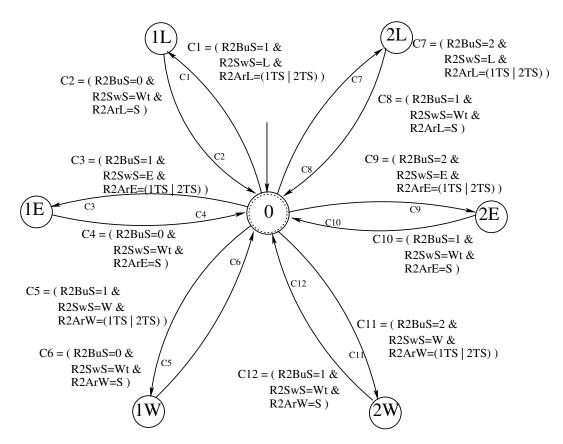

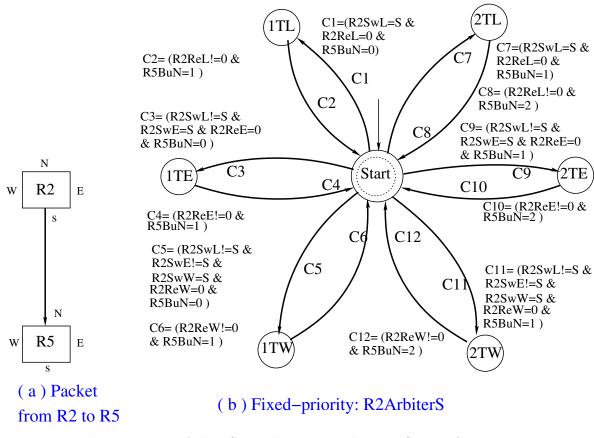

| 3.6  | R2ArbiterS: Fixed-priority arbiter at S port of router R2                    | 57 |

| 3.7  | R2PriorityS (Round-robin priority generator at the S output port of router   |    |

|      | R2)                                                                          | 58 |

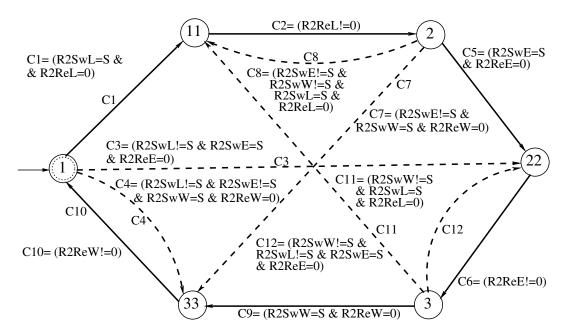

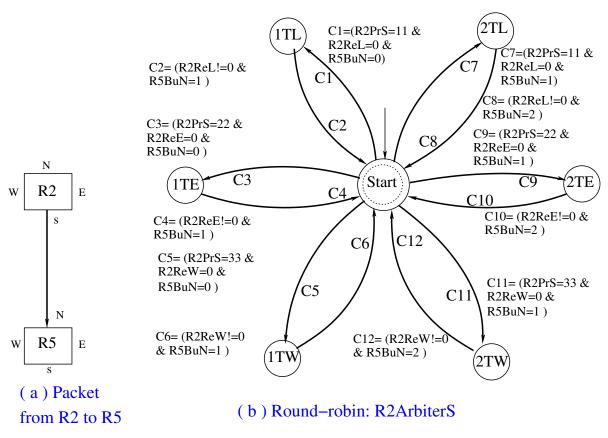

| 3.8  | R2ArbiterS (Round-robin arbiter at South port of Router R2)                  | 60 |

| 3.9  | Partitioning NoC: Active Windows for the Router R5 and R9                    | 68 |

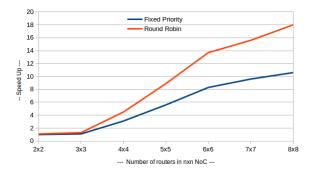

| 3.10 | Speed up with the increase in the number of routers                          | 70 |

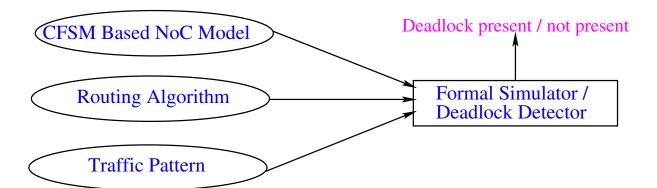

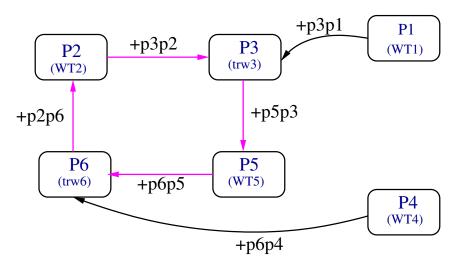

| 4.1  | Deadlock Detection using CFSM based NoC Model                                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

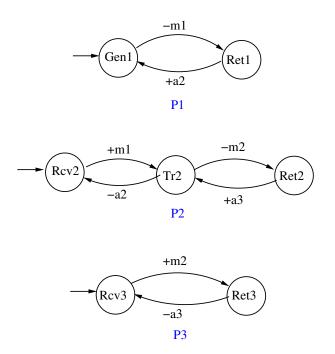

| 4.2  | Three CFSM processes communicating with each other                                                                                                                                                                                                                                                                        |

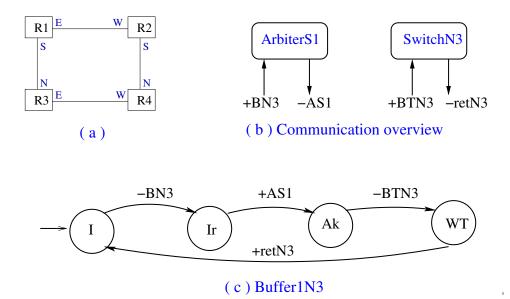

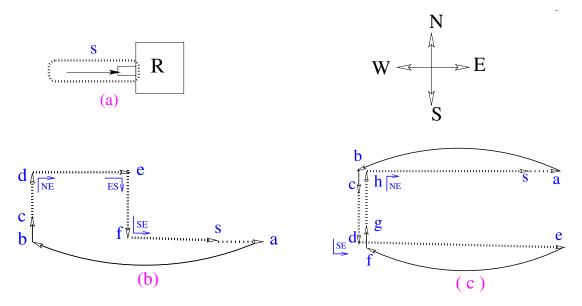

| 4.3  | Buffer with single slot: (a) 2x2 NoC as a reference for modeling (b) Overall communication for buffer at the North port of router R3 (c) CFSM model                                                                                                                                                                       |

|      | for buffer with capacity=1                                                                                                                                                                                                                                                                                                |

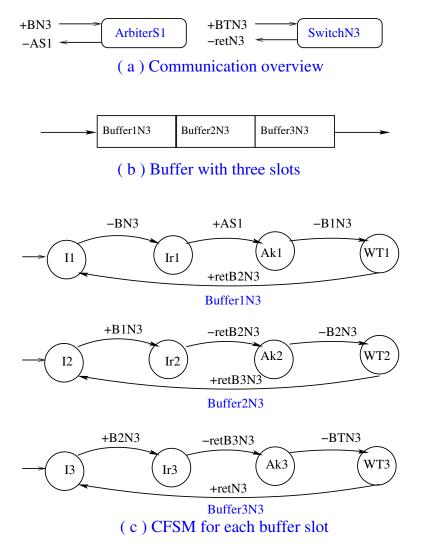

| 4.4  | Buffer with three slots: (a) Overall communication for buffer at the North port of router R3 (b) Three buffer slots as a FIFO (c) CFSM model for buffer with three slots                                                                                                                                                  |

| 4.5  | CFSM model for a switch: (a) Switch at the North port of router R3 (b)                                                                                                                                                                                                                                                    |

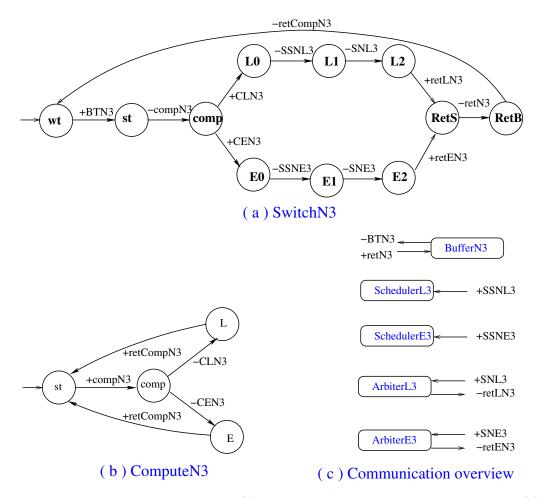

| 1.0  | Route computation (c) Communication overview for SwitchN3 with other<br>NoC components                                                                                                                                                                                                                                    |

| 4.6  | Arbiter and Scheduler at the South Port of Router R1: (a) CFSM model for                                                                                                                                                                                                                                                  |

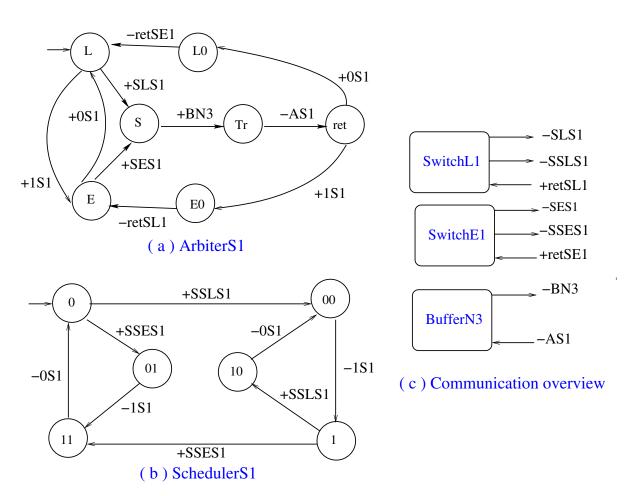

| 4.0  | Arbiter S1, (b) CFSM model for SchedulerS1, (c) Communication overview<br>for ArbiterS1                                                                                                                                                                                                                                   |

| 4.7  | Virtual channel: (a) Buffer with four slots, (b) Buffer restructuring for two                                                                                                                                                                                                                                             |

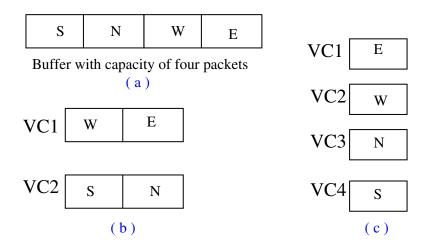

| 4.1  | virtual channels, (c) Buffer restructuring for four virtual channels                                                                                                                                                                                                                                                      |

| 4.8  | An example of delayed reception                                                                                                                                                                                                                                                                                           |

| 4.9  | CFSMs with Cyclic Dependency                                                                                                                                                                                                                                                                                              |

| 4.10 | Global State Transitions of CFSMs in Fig. 4.9                                                                                                                                                                                                                                                                             |

| 4.11 | Cyclic Dependency Graph for the CFSMs in Fig. 4.9                                                                                                                                                                                                                                                                         |

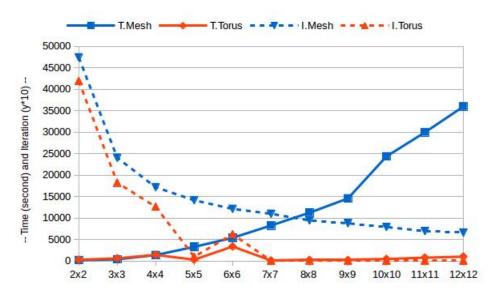

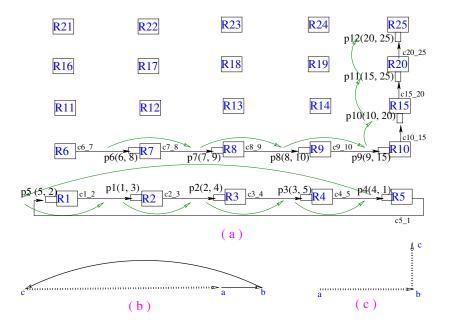

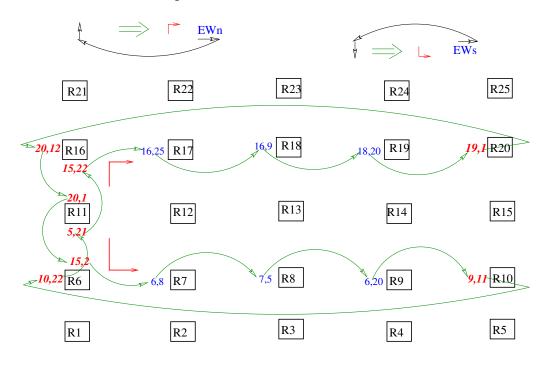

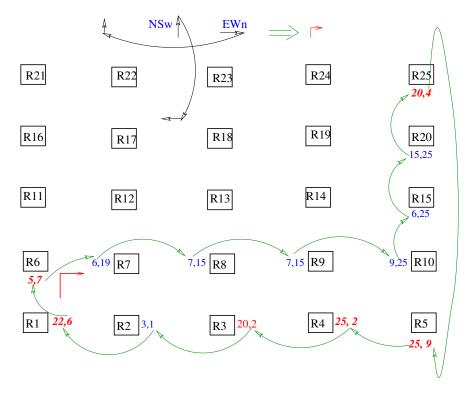

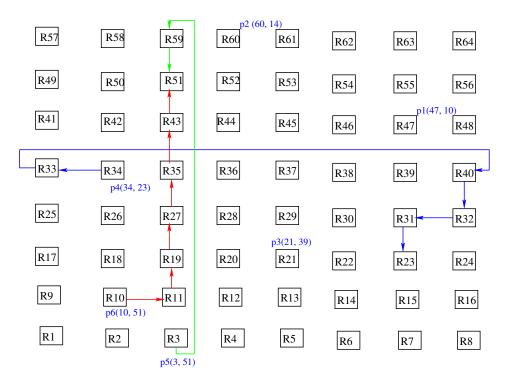

|      | Experiment I: XY Algorithm on Mesh and Torus NoCs with traffic pattern                                                                                                                                                                                                                                                    |

|      | of 100000 packets. Run-time increases with the increase of NoC size if there                                                                                                                                                                                                                                              |

|      | is no deadlock. Deadlock is detected in Torus NoC if NoC size is bigger than                                                                                                                                                                                                                                              |

|      | $4x4. \ldots \ldots$                                                                                                                                                                               |

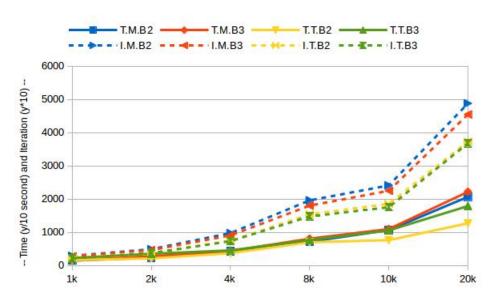

| 4.13 | Experiment II: XY Algorithm on a 3x3 NoC (Mesh and Torus) applying<br>traffic patterns of different sizes. (T.M.B2: Time taken by Mesh with buffer<br>size 2, T.T.B2: Time taken by Torus with buffer size 2, I.M.B2: Iterations<br>for Mesh with buffer size 2, I.T.B2: Iterations for Torus with buffer size 2 etc.)110 |

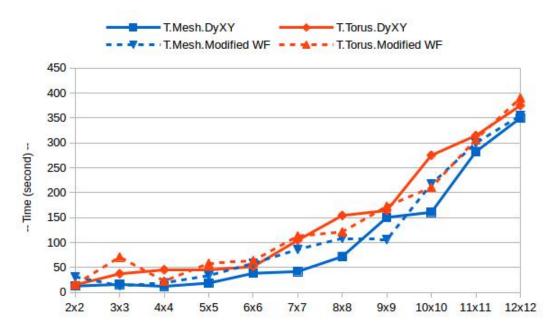

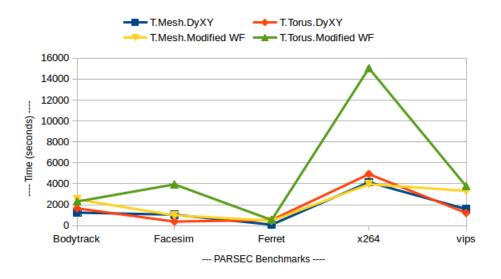

| 4.14 | Experiment III: Dynamic XY Algorithm and Modified West-First Algorithm                                                                                                                                                                                                                                                    |

|      | (NW Turn Restricted) on traffic patterns of 100000 packets. Deadlock detec-                                                                                                                                                                                                                                               |

|      | tion time depends on the pattern of the input traffic                                                                                                                                                                                                                                                                     |

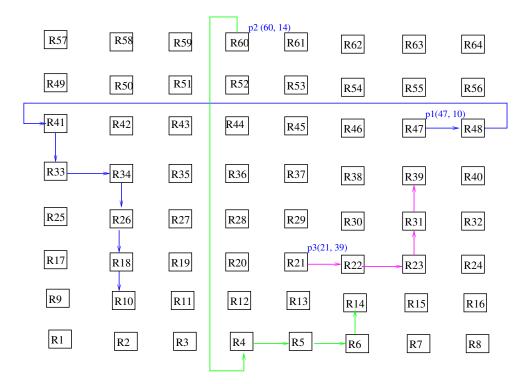

| 4.15 | Deadlock Detection: Dynamic XY Algorithm and Modified West-First Al-<br>gorithm (NW Turn Restricted) using PARSEC benchmarks in an 8x8 Mesh                                                                                                                                                                               |

|      | NoC                                                                                                                                                                                                                                                                                                                       |

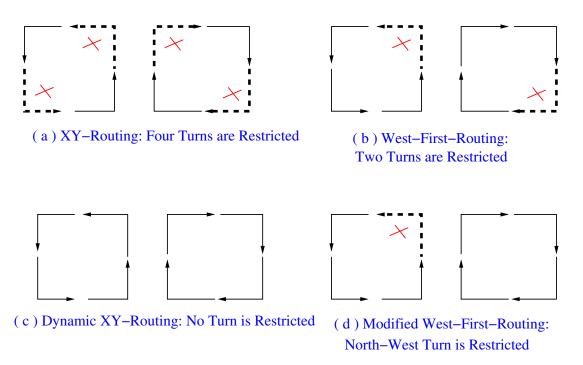

| 4.16 | Turn model for routing algorithms: (a) XY-routing, (b) Dynamic XY-routing,                                                                                                                                                                                                                                                |

|      | (c) West-First routing and (d) Modified West-First routing                                                                                                                                                                                                                                                                |

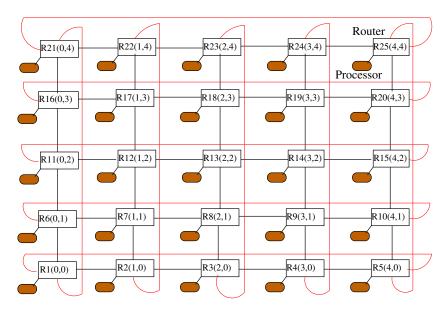

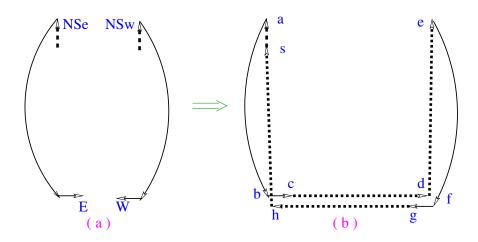

| 5.1  | Visualising $5 \mathrm{x5}$ Torus NoC as a combination of Mesh sub-network and wrap<br>around | ł          |

|------|-----------------------------------------------------------------------------------------------|------------|

|      | channels                                                                                      | 20         |

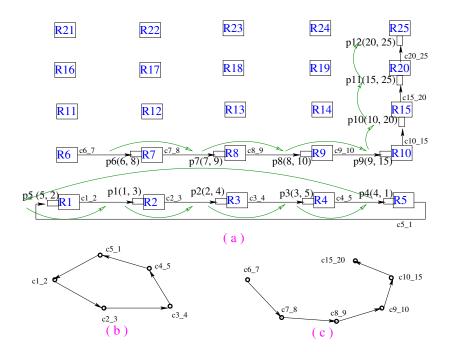

| 5.2  | (a) Resource dependency scenarios for a set of packets (source and destina-                   |            |

|      | tion are shown in the bracket), (b) Channel Dependency Graph representing                     |            |

|      | deadlock scenario, (c) Channel Dependency Graph showing a resource de-                        |            |

|      | pendency                                                                                      | 21         |

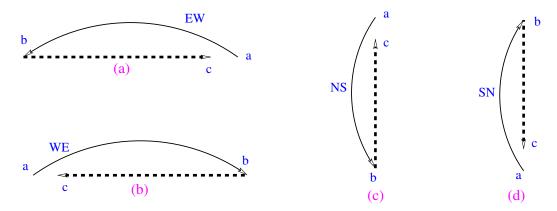

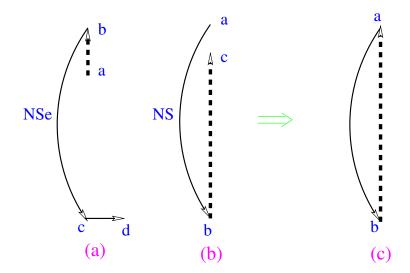

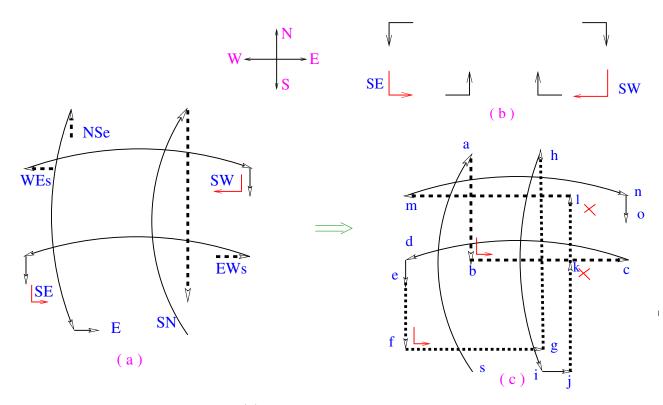

| 5.3  | Turn model: (a) Anti-clockwise cycle, (b) Clockwise cycle, (c) XY-Turns, (d)                  |            |

|      | YX-Turns                                                                                      | 24         |

| 5.4  | Wraparound channels in a single row of a $\ 3x3$ and $\ 4x4$ Torus NoC $\ .$ 12               | 25         |

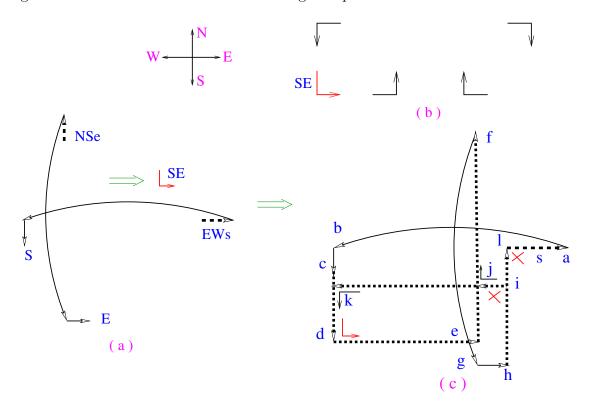

| 5.5  | (a) Potential Deadlock, (b) Deadlock Avoidance, (c) EWn Arc, (d)EWs Arc. 12                   | 28         |

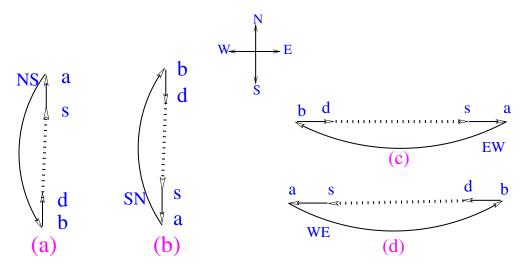

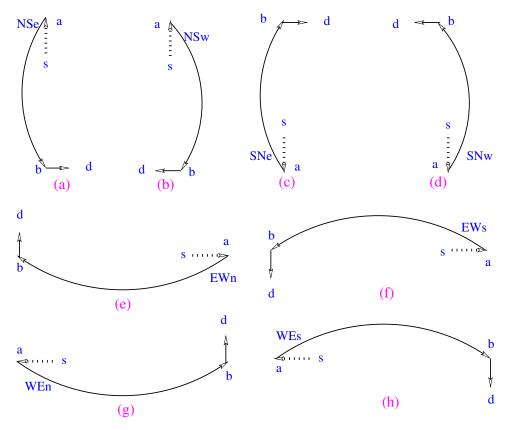

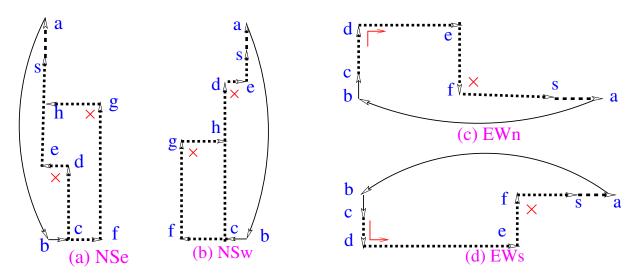

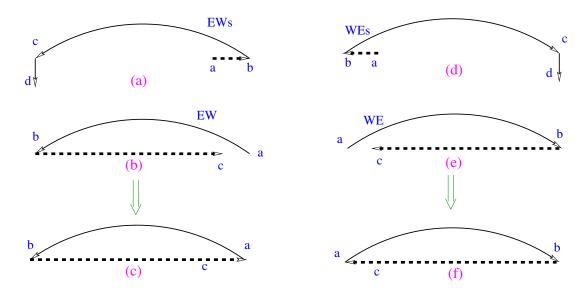

| 5.6  | Wraparound channels: (a) NS, (b) SN, (c) EW, (d) WE                                           | 29         |

| 5.7  | Arc model: Eight possible Arcs in Torus NoC                                                   | 30         |

| 5.8  | (a) Channel-buffer combination as a vertex, (b) Dependency cycle with EWn,                    |            |

|      | (c) Dependency cycle with EWn and EWs                                                         | 31         |

| 5.9  | (a) Resource dependency for a set of packets (source and destination are                      |            |

|      | shown in the bracket, b) Directional Dependency Graph representing a dead-                    |            |

|      | lock scenario, (c) Directional Dependency Graph representing a resource de-                   |            |

|      | pendency scenario                                                                             | 34         |

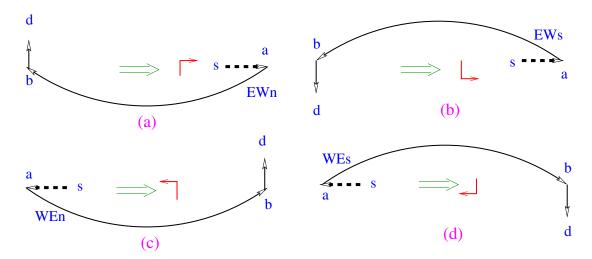

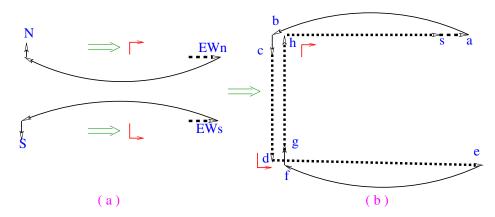

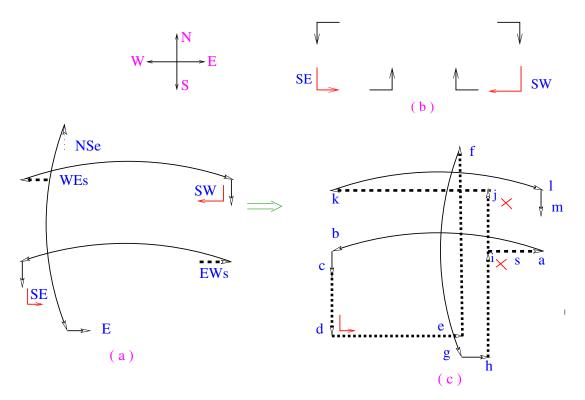

| 5.10 | Additional Turns introduced with respect to XY-Turns a) EWn Arc adds NE                       |            |

|      | Turn, b) EWs Arc adds SE Turn, c) WEn Arc adds NW Turn, and d) WEs                            |            |

|      | Arc adds SW Turn                                                                              | 36         |