Performance and Lifetime Enhancement of Non-Volatile Memory Caches

Sivakumar S.

# Performance and Lifetime Enhancement of Non-Volatile Memory Caches

Thesis submitted in partial fulfilment of the requirements for the degree of

# Doctor of Philosophy

in

COMPUTER SCIENCE AND ENGINEERING

by

Sivakumar S.

Under the supervision of

Dr. John Jose

DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

INDIAN INSTITUTE OF TECHNOLOGY GUWAHATI

January 2025

## To my family, teachers, and friends

- who have always believed in and supported me.

### **DECLARATION**

I hereby certify that

- a. The work contained in this thesis is original and has been done by myself and the general supervision of my supervisor.

- b. The work has not been submitted to any other institute for any degree or diploma.

- c. Whenever I have used materials (data, theoretical analysis, results) from other sources, I have given due credit by citing them in the text of the thesis and giving their details in the references. Elaborate sentences used verbatim from published work have been clearly identified and quoted.

- d. No part of this thesis can be considered plagiarism to the best of my knowledge and understanding and take complete responsibility if any complaint arises.

Date: 19 / 01 / 2025 Sivakumar S.

Place: Guwahati, India

### भारतीय प्रौद्योगिकी संस्थान गुवाहाटी

#### INDIAN INSTITUTE OF TECHNOLOGY GUWAHATI

Department of Computer Science & Engineering

Dr. John Jose Associate Professor johnjose@iitg.ac.in http://www.iitg.ac.in/johnjose/

### THESIS CERTIFICATE

This is to certify that the thesis entitled **Performance and Lifetime Enhancement of Non-Volatile Memory Caches** being submitted by **Sivakumar S.** to the Department of Computer Science and Engineering, Indian Institute of Technology Guwahati, is a record of bonafide research work carried out by him under my supervision and is worthy of consideration for the award of the degree of Doctor of Philosophy of the Institute.

To the best of my knowledge, no part of the work reported in this thesis has been presented for the award of any degree at any other institution.

Date: 19 / 01 / 2025

Place: Guwahati, India

Dr. John Jose

(Thesis Supervisor)

### ACKNOWLEDGMENTS

I embarked on my journey at IIT Guwahati in 2016 as a Project Engineer under Dr.John Jose, whose guidance and encouragement inspired me to pursue a PhD. His unwavering belief in my potential and his advice motivated me to explore the world of research. In June 2017, I was selected for the PhD program, and this decision marked a turning point in my life.

Dr. John Jose has been more than just a supervisor; he has been a true mentor. He provided me with the freedom to explore my research interests and offered numerous opportunities to develop both my technical and non-technical skills. My first international travel experience was under his guidance, an experience that I will cherish forever. I am deeply grateful for his continuous support, mentorship, and invaluable experiences that have shaped my academic journey.

In December 2017, I attended a GIAN course at IIT Madras by Prof. Vijaykrishnan Narayanan from the Department of Computer Science and Engineering at Pennsylvania State University. His insightful talk sparked my interest in exploring Non-Volatile Memories. I had the opportunity to interact with him again during his visit to IIT Guwahati in August 2022. Despite his busy schedule, Prof. Narayanan generously provided regular guidance and critical inputs, which eventually led to a publication with him. I sincerely thank him for his support and look forward to future collaborations.

I want to thank my doctoral committee members: Chairperson Prof. Jatindra Kumar Deka, Dr. Aryabartta Sahu, and Dr. Moumita Patra. Their valuable inputs and suggestions throughout the course of my PhD were instrumental in shaping the direction of my research. I want to extend my gratitude to all teaching and non-teaching staff of the Department of Computer Science and Engineering, especially Prof. T. Venkatesh and Prof. Sukumar Nandi for their help and support.

The inception of the MARS (Multicore Architecture Research and Systems) Lab in 2016 was another milestone in this journey. I was honoured to be among its first members alongside Abhijit, Dipika, and Manjari. The camaraderie and collaboration within the lab were instrumental in my development. Abhijit and Dipika's inputs and guidance were not only relevant but continue to motivate and inspire me to this day. Manju and Amit, who joined us later, have supported us. Manju, like a caring elder sister, was always concerned about my well-being, while Amit, though silent, has been accommodating and trustworthy. In the final phase of my PhD, the support of the new "Martians" – Syam, Vivekananda, and Rajeswari – was invaluable. Their

assistance, encouragement, and camaraderie helped me navigate the challenges of this period, making the journey more manageable. My campus life at IIT Guwahati was memorable, thanks to our group "Kameng Gadagam", which we formed based on our hostel. Al Ameen and Abdul Khader have always been with me; even now, they remain like brothers. I also fondly remember other members of the group – Dr Vivek Venugopal, Muhammad Shafeeque, Kiran, Joe Augustine, Ann Sheryl, and Albin – who made my stay in Guwahati a funny and unforgettable experience.

I am deeply grateful to all my teachers from school to college, who have played a crucial role in shaping my academic journey. I want to mention Prof. Rekha James from Cochin University of Science and Technology, who motivated and supported me in pursuing a PhD, and Mrs. Jyothi Sukumaran, who first taught me electronics at the school level and sparked my interest in the subject. My best friends, Arun Antony, Francis Amal, and Vishnu Lal, have been my constants for over two decades, always there for me in my ups and downs. Our enduring friendship has been a source of strength and joy. Finally and most importantly, I express my deepest gratitude to my parents, who always believed in me and provided the best possible support. I would like to thank my understanding brother and my wife, Divya, who stood firmly by my side through all the ups and downs during these years. Thank you all for making my life a good one.

To all those who have been part of this journey, whether mentioned here or not, your contributions have been significant, and I extend my heartfelt gratitude. This thesis is a testament to the collective efforts, support, and encouragement I have received throughout this remarkable journey.

Guwahati, January 2025

Sivakumar S.

### ABSTRACT

In recent decades, technological advancements have led to the emergence of numerous applications requiring increased computing power and larger on-chip and off-chip memory capacities. However, the memory technologies are not scaling up with the computational throughput of modern multi-core processors. Due to their low packaging density and high leakage power, traditional memory technologies like SRAM and DRAM face challenges in meeting substantial on-chip memory demands. Researchers have developed alternative solutions to address the growing need for memory, such as emerging non-volatile memory technologies like STT-RAM, PCM, and ReRAM. These techniques have the advantages of high packaging density, low power consumption and non-volatility. NVMs can be realized as Single Level Cells (SLC) or Multi Level Cells (MLC). SLCs store one bit of information per cell, whereas MLCs can store more than one bit per memory cell. The package density of NVMs can be further improved by using MLC NVMs instead of SLC NVMs.

Despite their advantages, these memory technologies have limited write endurance, high write latency and high write energy consumption. This highlights the necessity for policies that reduce write operations or evenly distribute them across memory cells, extending the lifetime of memory by mitigating premature wear-out caused by frequent writes. Considering the limitations of NVMs that need to be addressed in order to use them as cache memory, the thesis proposes optimization techniques for SLC and MLC NVM caches. The proposed techniques perform better than existing lifetime improvement techniques for SLC and MLC NVMs. The thesis shows that the proposed technique extends lifetime of MLC NVMs comparable to that of SLC NVMs with less area overhead.

# Table of Contents

|          |      |                                                               | Page |

|----------|------|---------------------------------------------------------------|------|

|          | List | of Figures                                                    | iv   |

|          | List | of Tables                                                     | viii |

|          | List | of Acronyms                                                   | xi   |

| 1        | Intr | roduction                                                     | 1    |

|          | 1.1  | Thesis Motivation                                             | . 2  |

|          | 1.2  | Thesis Contributions                                          | . 5  |

|          |      | 1.2.1 Write Aware Last Level Non-Volatile Caches (WALL-NVC) . | . 7  |

|          |      | 1.2.2 Virtually Split Last Level Non-Volatile Cache           | . 7  |

|          |      | 1.2.3 Trace buffer Assisted Last Level Non-Volatile Cache     | . 8  |

|          | 1.3  | Thesis Organization                                           | . 9  |

| <b>2</b> | Bac  | kground                                                       | 11   |

|          | 2.1  | Emerging Memory Technologies                                  | . 11 |

|          | 2.2  | Related Works                                                 | . 18 |

| 3        | Exp  | perimental Setup                                              | 24   |

|          | 3.1  | Adopted simulation environment                                | . 24 |

|          | 3.2  | Benchmark Programs                                            | . 26 |

|          | 3.3  | Performance Metrics                                           | . 28 |

|          |      | 3.3.1 Intra and Inter Set Write Variation                     | . 28 |

|          |      | 3.3.2 Relative Lifetime                                       | . 29 |

|          |      | 3.3.3 Cache Hit Rate                                          | . 29 |

|          |      | 3.3.4 Average Memory Access Time                              | . 30 |

| 4 | Wri | te Awa                 | are Last Level Non-Volatile Cache        | 31 |  |  |  |

|---|-----|------------------------|------------------------------------------|----|--|--|--|

|   | 4.1 | Introd                 | luction                                  | 31 |  |  |  |

|   | 4.2 | Motiv                  | ation                                    | 32 |  |  |  |

|   | 4.3 | 4.3 Proposed technique |                                          |    |  |  |  |

|   |     | 4.3.1                  | Least Recently Used Cold Block (LRU-CB)  | 34 |  |  |  |

|   |     | 4.3.2                  | Impact of LRU-CB with Write Distribution | 35 |  |  |  |

|   |     | 4.3.3                  | Write Distribution in WALL-NVC           | 36 |  |  |  |

|   | 4.4 | Exper                  | imental Setup and Result Analysis        | 39 |  |  |  |

|   |     | 4.4.1                  | Impact on Write Variation                | 40 |  |  |  |

|   |     | 4.4.2                  | Impact on Relative Lifetime              | 43 |  |  |  |

|   |     | 4.4.3                  | Impact on IPC                            | 45 |  |  |  |

|   |     | 4.4.4                  | Sensitivity Analysis                     | 46 |  |  |  |

|   |     | 4.4.5                  | Overhead Analysis                        | 49 |  |  |  |

|   | 4.5 | Concl                  | usion                                    | 50 |  |  |  |

| 5 | Vir | tually                 | Split Last Level Non-Volatile Cache      | 51 |  |  |  |

|   | 5.1 | Introd                 | luction                                  | 51 |  |  |  |

|   | 5.2 | Motiv                  | ation                                    | 52 |  |  |  |

|   | 5.3 | Propo                  | sed Technique - ViSC                     | 53 |  |  |  |

|   |     | 5.3.1                  | Virtually Split Cache (ViSC)             | 54 |  |  |  |

|   |     | 5.3.2                  | Enhanced-ViSC                            | 59 |  |  |  |

|   |     | 5.3.3                  | Protean-ViSC                             | 62 |  |  |  |

|   | 5.4 | Exper                  | imental Setup and Result Analysis        | 66 |  |  |  |

|   |     | 5.4.1                  | Impact on Relative Lifetime              | 66 |  |  |  |

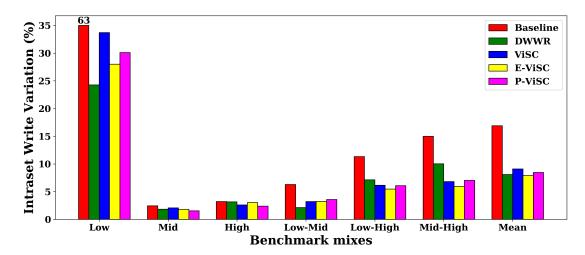

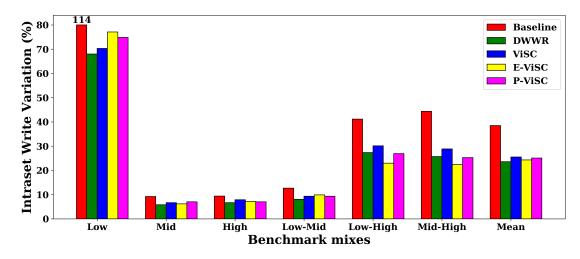

|   |     | 5.4.2                  | Impact on Intra-set variation            | 73 |  |  |  |

|   |     | 5.4.3                  | Impact on Inter-set variation            | 78 |  |  |  |

|   |     | 5.4.4                  | Impact on IPC                            | 78 |  |  |  |

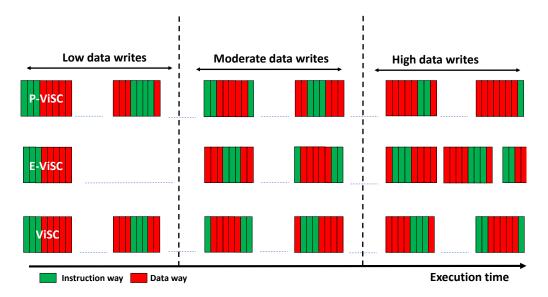

|   |     | 5.4.5                  | Impact on Execution Time Distribution    | 79 |  |  |  |

|   |     | 5.4.6                  | Overhead Analysis                        | 81 |  |  |  |

|   | 5.5 | Concl                  | usion and Future scope                   | 89 |  |  |  |

| 6 | Tra  | ce bufl | fer Assisted Last Level Non-Volatile Caches               | 84  |

|---|------|---------|-----------------------------------------------------------|-----|

|   | 6.1  | Introd  | luction                                                   | 84  |

|   | 6.2  | Motiv   | ation                                                     | 85  |

|   | 6.3  | Propo   | sed Techniques                                            | 86  |

|   |      | 6.3.1   | Embedded Trace Buffer (ETB)                               | 87  |

|   |      | 6.3.2   | TANC Organization                                         | 87  |

|   |      | 6.3.3   | TANC variants with write minimization only                | 91  |

|   |      | 6.3.4   | TANC Variants With Write Minimization And Wear-leveling . | 93  |

|   |      | 6.3.5   | TANC with Skip cache                                      | 94  |

|   | 6.4  | Exper   | imental Setup and Result Analysis                         | 96  |

|   |      | 6.4.1   | Impact on Relative Lifetime                               | 97  |

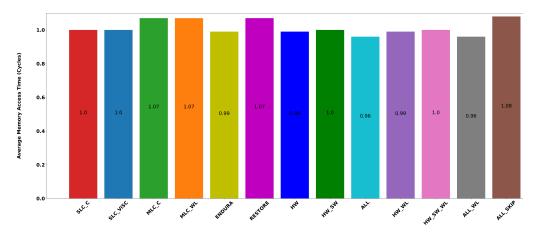

|   |      | 6.4.2   | Impact on Average Memory Access Time                      | 100 |

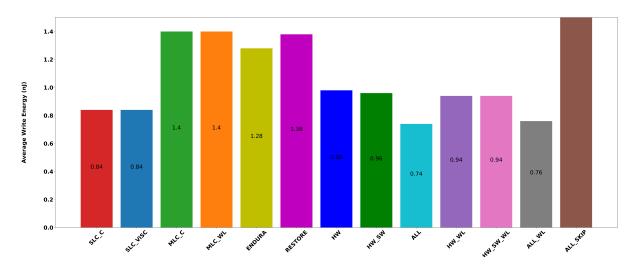

|   |      | 6.4.3   | Impact on Write Energy                                    | 102 |

|   |      | 6.4.4   | Impact on Hard-way Writes                                 | 103 |

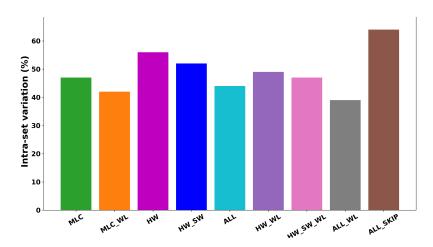

|   |      | 6.4.5   | Impact on Intra-set and Inter-set variations              | 105 |

|   |      | 6.4.6   | Overhead Analysis                                         | 107 |

|   | 6.5  | Concl   | usion and Future works                                    | 107 |

| 7 | Con  | clusio  | n and Future Work                                         | 109 |

|   | 7.1  | Thesis  | Summary                                                   | 109 |

|   | 7.2  | Future  | e Research Directions                                     | 110 |

|   | Bib  | liograp | ohy                                                       | 111 |

|   | List | of Pu   | blications                                                | 119 |

# List of Figures

|     | P                                                                                                                                                                                                                 | age |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1 | Memory Hierarchy                                                                                                                                                                                                  | 2   |

| 1.2 | Intra-set write variation for L2 cache for various benchmarks                                                                                                                                                     | 4   |

| 1.3 | Overview of Thesis Contributions                                                                                                                                                                                  | 6   |

| 2.1 | Schematic representation of an STT-RAM cell                                                                                                                                                                       | 12  |

| 2.2 | Schematic representation of a PCM cell                                                                                                                                                                            | 13  |

| 2.3 | Schematic representation of a ReRAM cell                                                                                                                                                                          | 14  |

| 2.4 | Schematic representation of (a) SLC (b) Serial MLC and (c) Parallel MLC STT-RAM cell                                                                                                                              | 16  |

| 2.5 | Hard and Soft-bit states during different transitions of a MLC STT-RAM cell                                                                                                                                       | 17  |

| 2.6 | 4 bit cache lines in (a) Direct Mapping (b) Cell Split Mapping                                                                                                                                                    | 18  |

| 3.1 | High-level view of the main components in Ruby [Image source: gem5 documentation (https://www.gem5.org)]                                                                                                          | 25  |

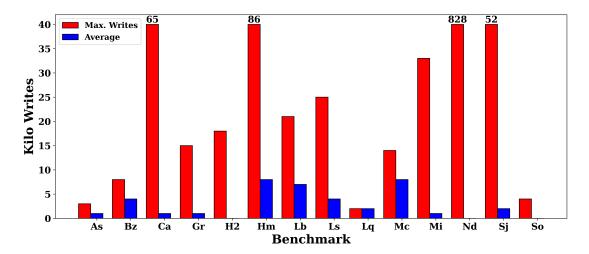

| 4.1 | Average and maximum writes per way (Kilo writes per 1 billion instructions) of various SPEC CPU2006 benchmarks: height difference between bars of a given benchmark indicates intensity of write level variations | 33  |

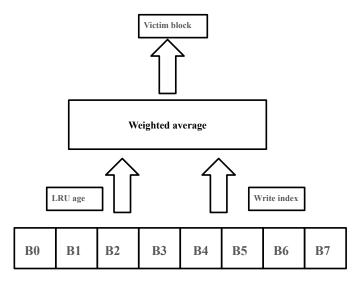

| 4.2 | Schematic representation of victim block selection using LRU-CB policy in Set A of an 8-way set associative cache                                                                                                 | 35  |

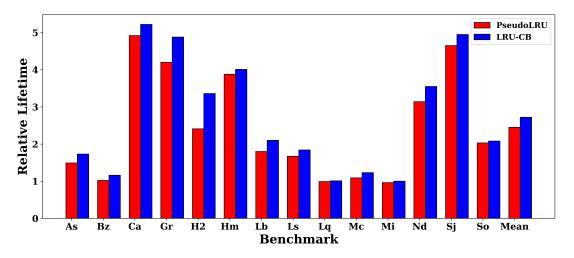

| 4.3 | Comparison of relative lifetime of NVM based L2 cache using Equal-Writes with Pseudo LRU and LRU-CB replacement policies                                                                                          | 36  |

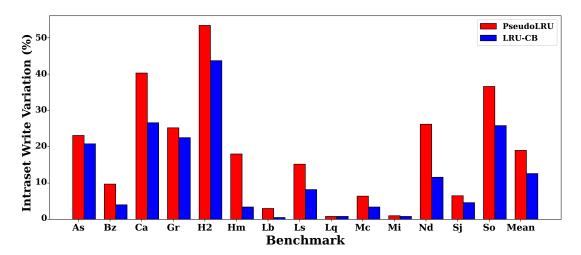

| 4.4 | Comparison of intra-set variation of NVM based L2 cache using Equal-Writes with Pseudo LRU and LRU-CB replacement policies                                                                                        | 37  |

| 4.5 | Comparison of hit rate of NVM based L2 cache using EqualWrites with Pseudo LRU and LRU-CB replacement policies                                                                                                    | 38  |

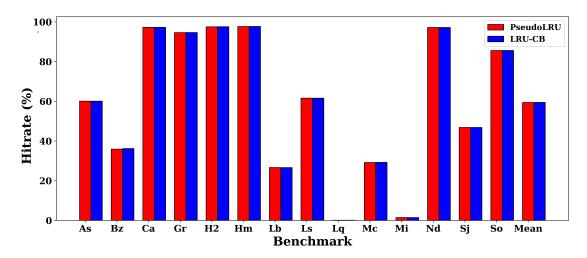

| 4.6  | Sample counter updating of WALL-NVC for threshold value, $T=50$ .                                         | 36 |

|------|-----------------------------------------------------------------------------------------------------------|----|

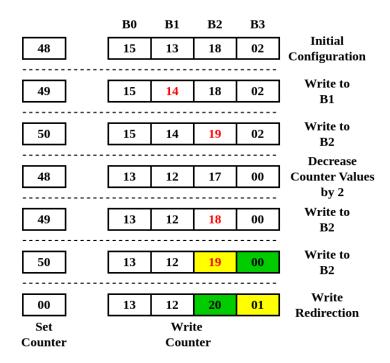

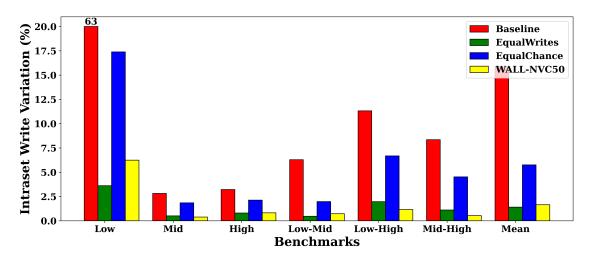

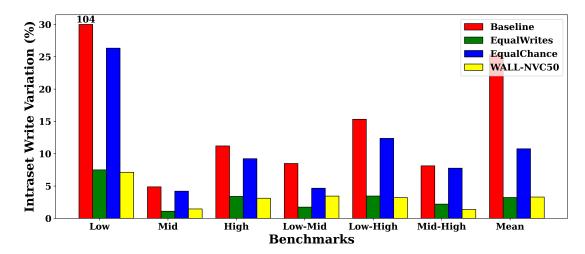

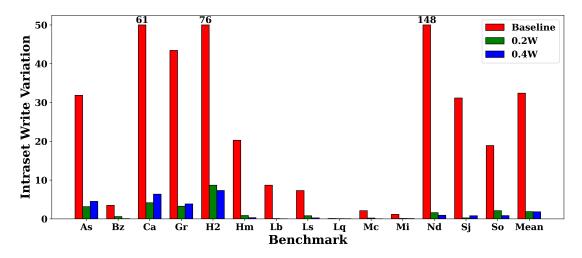

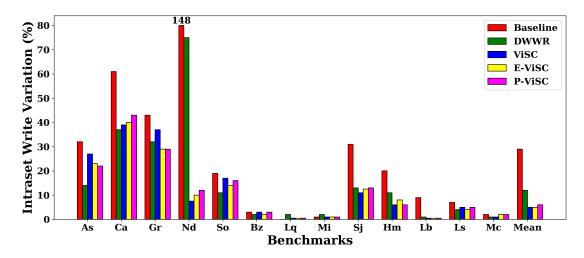

| 4.7  | Comparison of $IntraV$ for various NVM architectures in unicore system of L2 cache size 512KB             | 40 |

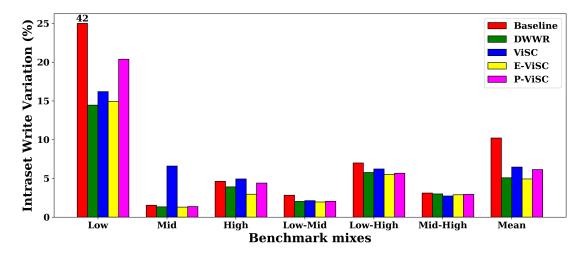

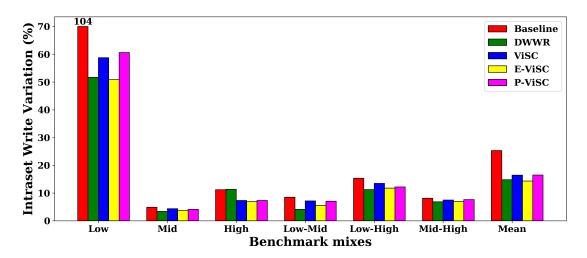

| 4.8  | Comparison of $IntraV$ for various NVM architectures in dual-core system of L2 cache size 512KB           | 41 |

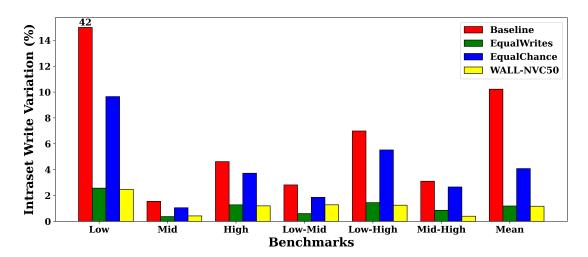

| 4.9  | Comparison of $IntraV$ for various NVM architectures in quad-core system L2 cache size 512KB              | 41 |

| 4.10 | Comparison of $IntraV$ for various NVM architectures in unicore system of L2 cache size 2MB               | 42 |

| 4.11 | Comparison of $IntraV$ for various NVM architectures in dual-core system L2 cache size 2MB                | 42 |

| 4.12 | Comparison of $IntraV$ for various NVM architectures in quad-core system L2 cache size 2MB                | 43 |

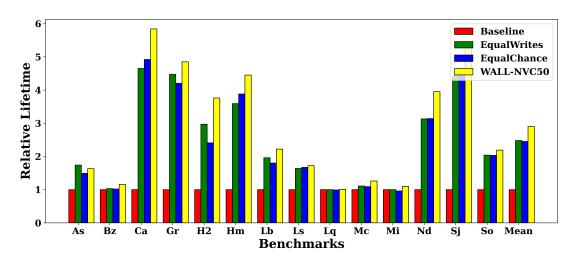

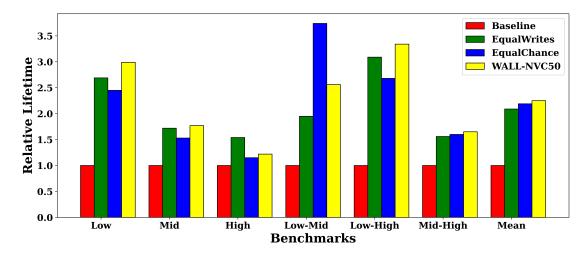

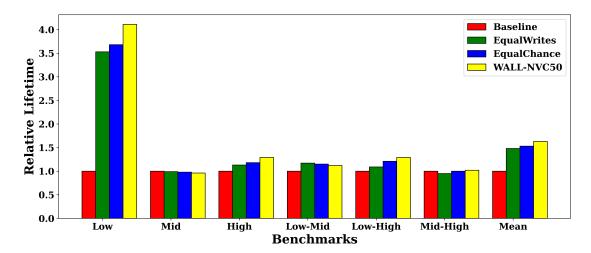

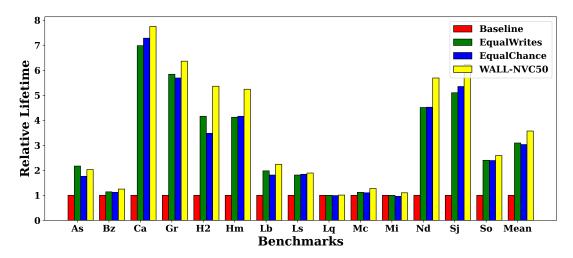

| 4.13 | Comparison of relative lifetime for various NVM architectures in unicore system of L2 cache size 512KB    | 44 |

| 4.14 | Comparison of relative lifetime for various NVM architectures in dual-core system L2 cache size 512KB     | 45 |

| 4.15 | Comparison of relative lifetime for various NVM architectures in quad-<br>core system L2 cache size 512KB | 46 |

| 4.16 | Comparison of relative lifetime for various NVM architectures in unicore system of L2 cache size 2MB      | 47 |

| 4.17 | Comparison of relative lifetime for various NVM architectures in dual-<br>core system L2 cache size 2MB   | 47 |

| 4.18 | Comparison of relative lifetime for various NVM architectures in quad-<br>core system                     | 48 |

| 4.19 | Comparison of $IntraV$ for WALL-NVC variants in unicore system                                            | 48 |

| 4.20 | Comparison of relative lifetime for WALL-NVC variants in unicore system                                   | 49 |

| 4.21 | Comparison of LLC hit rate for WALL-NVC variants in unicore system                                        | 49 |

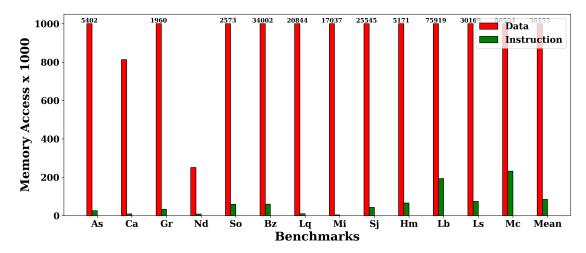

| 5.1  | L2 cache access pattern for different benchmark applications                                              | 53 |

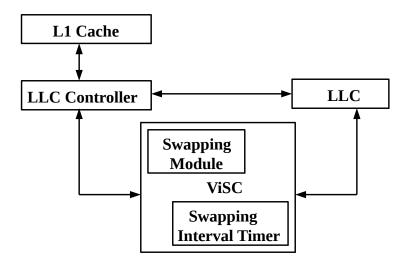

| 5.2  | L1 cache - LLC interaction through the proposed ViSC module                                               | 54 |

| 5.3  | Organization of a set of 8-way set associative cache in ViSC architecture                                 | 57 |

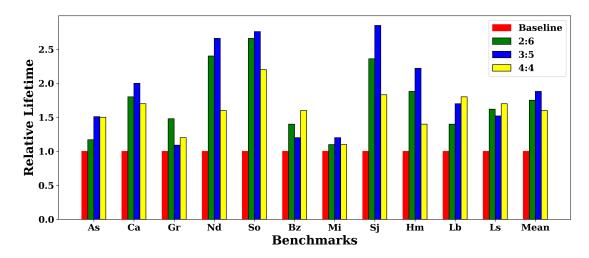

| 5.4  | Relative lifetime values of different partition ratios of ViSC enabled L2 cache for various benchmarks                  | 59 |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

| 5.5  | Relative lifetime values of different reorganization intervals (cycles) of ViSC enabled L2 cache for various benchmarks | 59 |

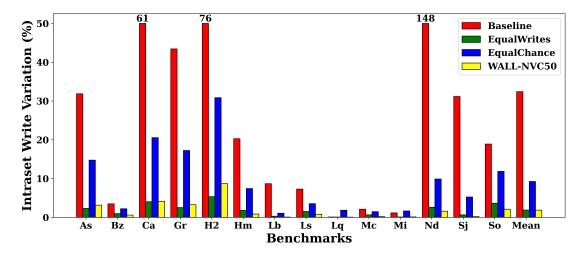

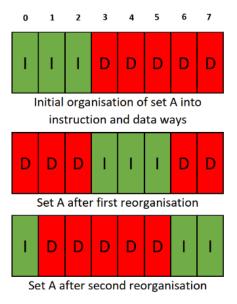

| 5.6  | Organisation of set A of eight-way set associative caches after each reorganization of proposed techniques              | 63 |

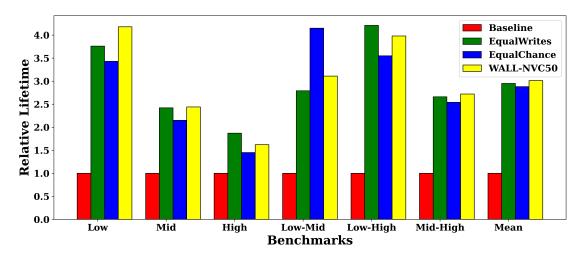

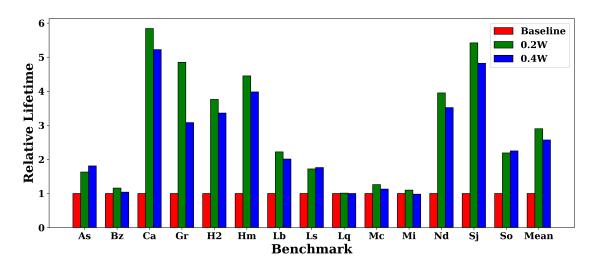

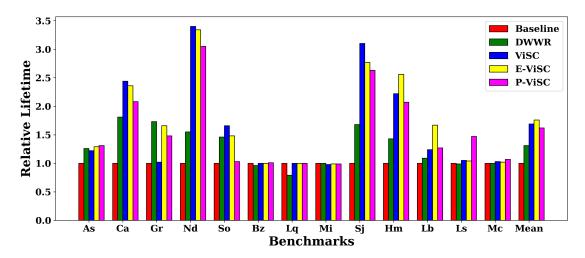

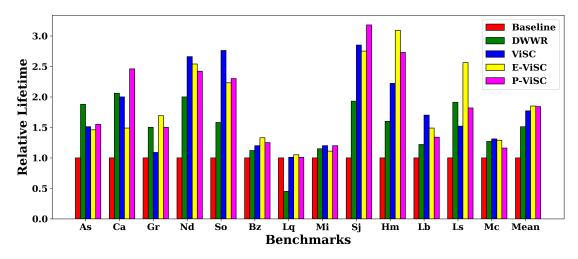

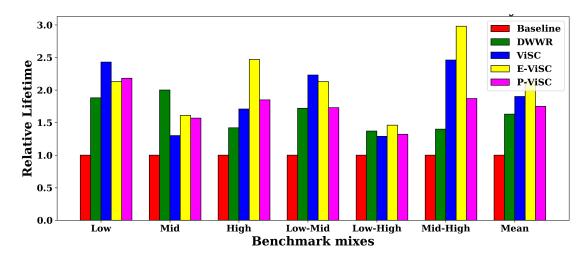

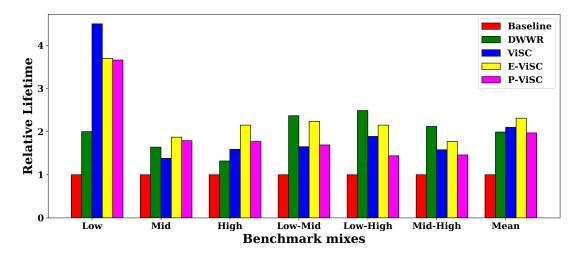

| 5.7  | Relative lifetime of 512KB 8-way set associative NVM L2 cache in a unicore system                                       | 67 |

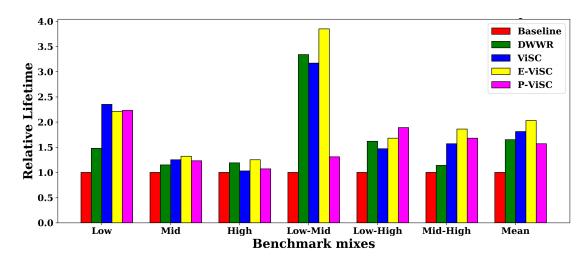

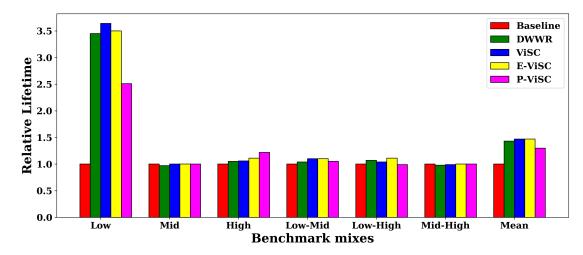

| 5.8  | Relative lifetime of 512KB 8-way set associative NVM L2 cache in a dual-core system                                     | 69 |

| 5.9  | Relative lifetime of 512KB 8-way set associative NVM L2 cache in a quad-core system                                     | 70 |

| 5.10 | Relative lifetime of 2MB 8-way set associative NVM L2 cache in a unicore system                                         | 70 |

| 5.11 | Relative lifetime comparison of 2MB 8-way set associative NVM L2 cache in a dual-core system                            | 71 |

| 5.12 | Relative life time comparison of 2MB 8-way set associative NVM L2 cache in a quad-core system                           | 71 |

| 5.13 | Relative lifetime of 512KB 16-way set associative NVM L2 cache in a unicore system                                      | 72 |

| 5.14 | Relative lifetime of 512KB 4-way set associative NVM L2 cache in a unicore system                                       | 72 |

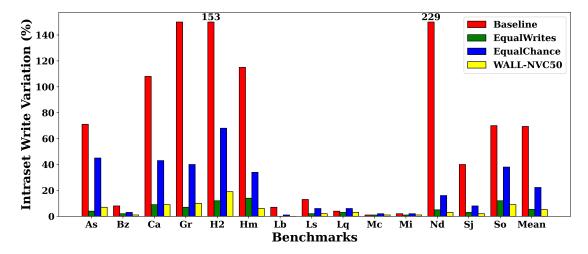

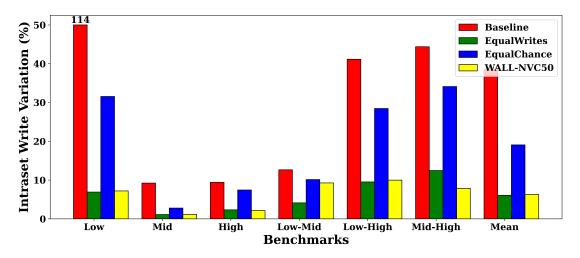

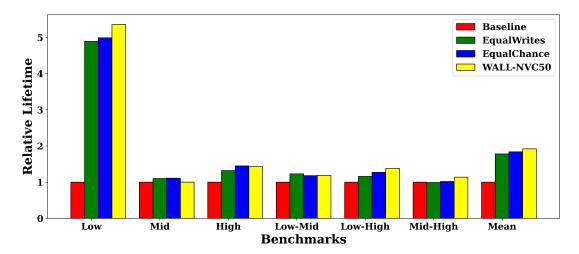

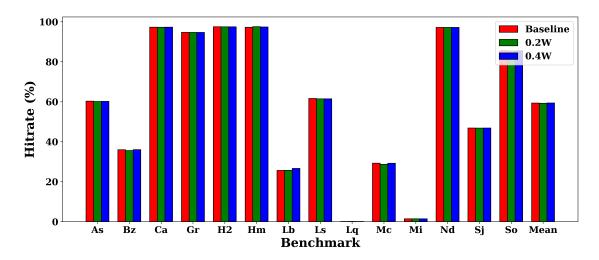

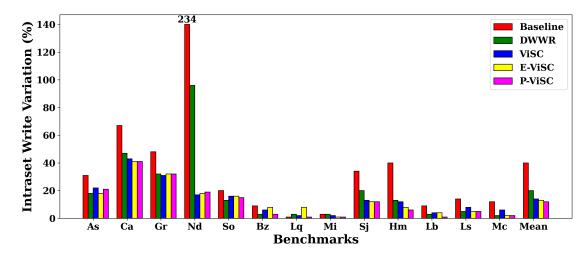

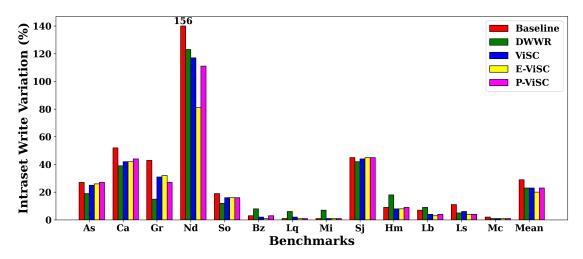

| 5.15 | Intra-set variation comparison of 512KB 8-way set associative NVM L2 cache in a unicore system                          | 73 |

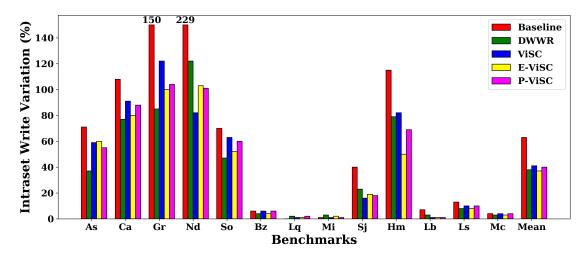

| 5.16 | Intra-set variation comparison of 2MB 8-way set associative NVM L2 cache in a unicore system                            | 74 |

| 5.17 | Intra-set variation comparison of 512KB 8-way set associative NVM L2 cache in a dual-core system                        | 75 |

| 5.18 | Intra-set variation comparison of 2MB 8-way set associative NVM L2 cache in a dual-core system                          | 75 |

| 5.19 | Intra-set variation comparison of 512KB 8-way set associative NVM L2 cache in a quad-core system                        | 76 |

#### LIST OF FIGURES

| 5.20 | Intra-set variation comparison of 2MB 8-way set associative NVM L2           |     |

|------|------------------------------------------------------------------------------|-----|

|      | cache in a quad-core system $\dots$                                          | 76  |

| 5.21 | Intra-set variation comparison of 512KB 16-way set associative NVM $$        |     |

|      | L2 cache in a unicore system                                                 | 77  |

| 5.22 | Intra-set variation comparison of $512\mathrm{KB}$ 4-way set associative NVM |     |

|      | L2 cache in a unicore system                                                 | 77  |

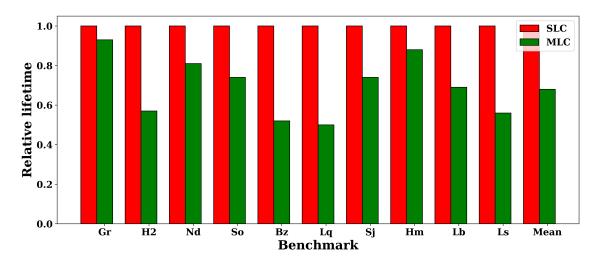

| 6.1  | Relative lifetime of SLC and MLC NVM LLC for various SPEC                    |     |

|      | CPU2006 benchmarks                                                           | 86  |

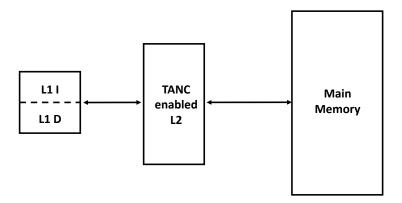

| 6.2  | Schematic diagram of memory hierarchy with TANC $\dots$                      | 88  |

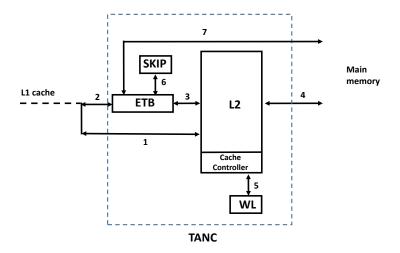

| 6.3  | Schematic representation of TANC enabled L2 cache                            | 89  |

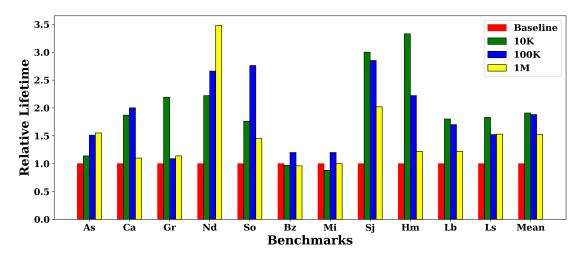

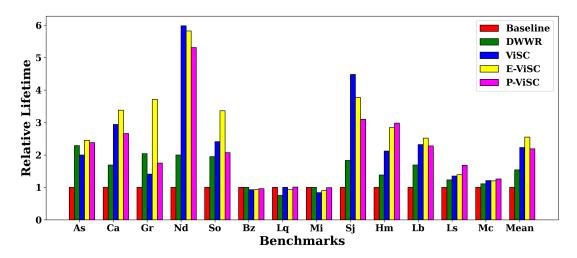

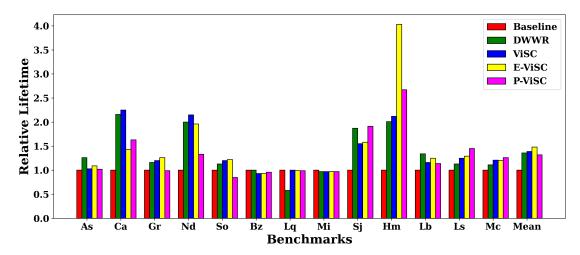

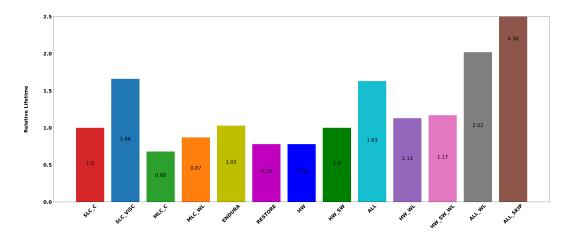

| 6.4  | Relative lifetime of various techniques                                      | 98  |

| 6.5  | Comparison of normalized AMAT (cycles) of various techniques $\ \ . \ \ .$   | 101 |

| 6.6  | Comparison of average write energy (nJ) of various techniques (shorter       |     |

|      | the bar, the better) $\dots$                                                 | 103 |

| 6.7  | Comparison of intra-set write variation of various TANC variants             |     |

|      | (shorter the bar, the better)                                                | 106 |

# List of Tables

|     | Pa                                                                                                 | age |

|-----|----------------------------------------------------------------------------------------------------|-----|

| 2.1 | Approximate values of device level properties for different memory technologies                    | 14  |

| 2.2 | Overview of proposed techniques and state-of-the-art approaches                                    | 23  |

| 3.1 | Selected SPEC CPU2006 Benchmarks with arconyms and category $$ .                                   | 27  |

| 4.1 | System Configuration                                                                               | 40  |

| 4.2 | Relative lifetime improvement (LT) and $IntraV$ of WALL-NVC for different threshold values         | 46  |

| 5.1 | Comparison of the proposed wear-leveling techniques                                                | 64  |

| 5.2 | Simulation parameters                                                                              | 66  |

| 5.3 | Percentage change in inter-set variation for various architectures and cache sizes under study     | 78  |

| 5.4 | Distribution of execution time (in %) of E-ViSC while running various benchmark mixes              | 80  |

| 5.5 | Distribution of execution time of P-ViSC while running various benchmark mixes (%)                 | 81  |

| 6.1 | Service of requests in TANC                                                                        | 90  |

| 6.2 | TANC variants and associated modules                                                               | 91  |

| 6.3 | Simulation parameters                                                                              | 97  |

| 6.4 | Comparison of relative lifetime of various techniques for different benchmark applications         | 99  |

| 6.5 | Comparison of normalized AMAT (cycles) of various techniques for different benchmark applications  | 102 |

| 6.6 | Comparison of average write energy (nJ) of various techniques for different benchmark applications | 104 |

#### LIST OF TABLES

| 6.7 | Average reduction of hard-way writes for TANC variants                | 104 |

|-----|-----------------------------------------------------------------------|-----|

| 6.8 | Comparison of intra-set write variation* of various TANC variants for |     |

|     | different benchmark applications                                      | 106 |

# List of Acronyms

Acronym Expansion

IoT Internet of Things

NVM Non Volatile Memory

STT-RAM Spin Transfer Torque Random Access Memory

PCM Phase Change Memory

ReRAM Resistive Random Access Memory

SRAM Static Random Access Memory

DRAM Dynamic Random Access Memory

IPC Instructions Per Cycle

LLC Last Level Cache

SLC Single Level Cell

MLC Multi Level Cell

DM Direct Mapping

CSM Cell Split Mapping

AMAT Average Memory Access Time

MPKI Misses Per Kilo Instructions

WPKI Writes Per Kilo Instructions

SWWR Static Window Write Restriction

DWWR Dynamic Window Write Restriction

ETB Embedded Trace Buffer

SoC System on Chip

### Introduction

$\mathbf{T}$  he amount of data we process daily has increased significantly over the last few decades. The rapid rise of IoT, on-demand video platforms, and data-intensive applications has drastically increased demand for high computing power and memory for end devices. The processor works at a higher clock speed compared to memory. To mitigate the speed mismatch between processor and memory, computing systems employ cache memory, a high-speed small memory near the processing element. Popular applications such as high-performance computing, gaming applications, and video streaming platforms exhibit spatial or temporal locality, or both. The spatial locality of an application refers to the tendency of an application to access contiguous memory locations in a short period. Matrix multiplication, video/audio streaming, and web browsing are popular applications that show spatial locality. On the other hand, the tendency of an application to access the same memory location for a short period is termed temporal locality. Using cache memory to keep frequently accessed blocks improves system performance by reducing memory access time, thereby improving CPU utilization. The small size of cache memories limits the blocks stored in them. The applications with large memory footprint demand larger on-chip/off-chip caches for better system performance. Unfortunately, conventional memory technologies

such as SRAM and DRAM are inadequate to meet the demand for large volumes of on- and off-chip memories, as they occupy a lot of space and dissipate more static power [1]. This led to a search for alternative technologies to replace them in various levels of memory hierarchy and non-volatile memory technologies. Spin Transfer Torque Random Access Memory (STT-RAM) [2] [3], Phase Change Memory (PCM) [4] and Resistive RAM [5] were found to be promising candidates. Although these technologies are more compact and have non-volatility, they have limitations, such as low write endurance, high write energy and latency. These issues are more severe in the case of Multi-Level Cell (MLC) NVMs than Single Level Cell (SLC) NVMs. Applications with non-uniform write patterns can cause some portions of memory to be more heavily written than others, which results in the early wearing out of corresponding non-volatile memory cells, owing to its limited write endurance. In the following sections of the thesis we discuss, how to make use of NVM techniques to realize cache memories using various optimization techniques in detail.

#### 1.1 Thesis Motivation

Over the past few decades, the demand for on-chip memory has increased due to data-intensive and compute-intensive applications, and the popular, conventional memory technologies are inadequate to meet this demand.

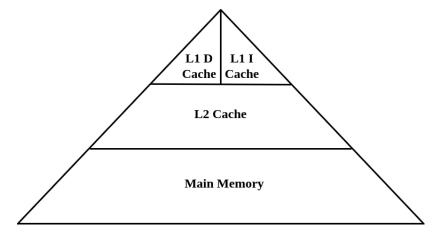

Figure 1.1: Memory Hierarchy

Figure 1.1 shows the memory hierarchy of a system with two levels of cache and

main memory. The size and latency increase as we move from L1 to the main memory in the memory hierarchy. L1 and L2 caches are realized using SRAM cells. L1 cache generally has a split architecture with separate space reserved for storing instructions and data blocks. L2 cache generally follows a unified architecture in which memory cells are not distinguished between instruction and data blocks. Realizing large LLCs (L2 or L3) using SRAM is challenging as SRAM cells occupy more on-chip space and dissipate more leakage power. So, we need better technology to realize large LLCs with less area and power overhead. As mentioned before, NVMs have the advantage of higher packaging density, low leakage power, and non-volatility compared to conventional SRAM and DRAM technologies. However, their low write endurance, high write energy and latencies are serious challenges that must be addressed when implemented as caches. As previously mentioned, applications without a well-distributed memory footprint may lead to frequent write operations concentrated on a few memory cells, resulting in premature wear out of memory cells. The early deterioration of specific memory cells can adversely impact the overall performance, reliability, and lifespan of the memory unit. A straightforward solution to address this issue is implementing a technique to ensure a uniform distribution of writes across the memory, irrespective of the application's memory footprint and is referred to as wear-leveling [1] [6]. Write minimization is another approach which minimize the number of writes to NVMs, thereby extending their lifetime [1]. In cache memories, variations in write operation can occur at different levels. Intra-set write variation refers to the variation within a set of cache memory, while inter-set write variation pertains to the variation across different sets. These variations are quantified using the coefficients of intra-set (IntraV) and inter-set (InterV) variation, as given in the equations below [6].

$$IntraV = \frac{1}{N \cdot Write_{avg}} \sum_{k=1}^{N} \sqrt{\frac{\sum_{l=1}^{M} (W_{k,l} - \sum_{m=1}^{M} \frac{W_{k,m}}{M})^{2}}{M-1}}$$

(1.1)

$$InterV = \frac{1}{Write_{avg}} \sqrt{\frac{\sum_{k=1}^{N} \left(\sum_{l=1}^{M} \frac{W_{k,l}}{M} - W_{avg}\right)^{2}}{N-1}}$$

(1.2)

Where N is number of sets in cache.

M is the number of ways in a set.

$W_{k,l}$  is the write count in set k and way l.

$Write_{avg}$  is average write count given by

$$Write_{avg} = \frac{\sum_{k=1}^{N} \sum_{l=1}^{M} W_{k,l}}{N \cdot M}$$

(1.3)

Write variation is a critical issue in designing cache or memory subsystems with

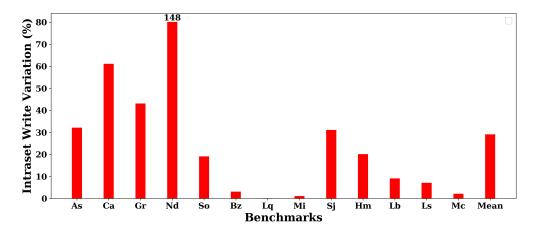

Figure 1.2: Intra-set write variation for L2 cache for various benchmarks

limited write endurance. Significant write variation can severely impact the product's lifetime, as a small subset of memory cells experiencing the highest write traffic can lead to the failure of the entire cache or memory subsystem, even if most cells remain far from wear-out. A large value of InterV indicates that cache lines in different sets experience vastly different write frequencies, often caused by applications with skewed address residency. Similarly, large IntraV value arises when one cache line within a set frequently receives write hits, absorbing a disproportionate number of writes, leaving the remaining M-1 lines in an M way associative cache with uneven write distribution.

Inter-set write variation can be mitigated by dynamic reallocation, where data is moved between sets, or by improving address mapping schemes [7] to balance write traffic across sets. However, addressing intra-set write variation is more challenging because the cache replacement policies (e.g., LRU) are designed to manage temporal

locality, not to distribute writes evenly across lines within a set. When a single cache line in a set wears out, the entire set may become unusable due to associative conflicts or invalid entries. This reduces the overall capacity of the cache and accelerates the degradation of the memory subsystem, especially in technologies with limited write endurance, like NVMs. Hence, intra-set write variation is a much more severe issue. The enhancement techniques discussed in this thesis primarily focus on improving the lifetime and performance of NVM caches by reducing the intra-set write variation.

The variation in writes within the sets of an L2 cache memory is illustrated in Figure 1.2, depicting various benchmark programs from the SPEC CPU2006 benchmark suite [details of the benchmarks are given in Chapter 3]. A higher intraset variation value suggests that certain blocks within a cache memory set experience more write accesses than others. This result emphasizes the importance of employing techniques to prevent repeated writes to specific blocks, either by bypassing them or distributing them throughout the memory.

#### 1.2 Thesis Contributions

As discussed earlier, incorporating NVMs in on-chip caches offers significant advantages. First, compared to SRAM and DRAM, NVMs provide denser storage due to their smaller cell size. This enables substantially larger caches, leading to lower cache miss rates and improved performance compared to SRAM-based caches. Second, NVM caches can significantly reduce energy consumption. Studies have shown that caches account for up to 50% of a microprocessor's energy usage [8], with leakage energy comprising as much as 80% of the total cache energy consumption [9]. By eliminating leakage energy in standby mode, NVMs can help to lower overall energy usage. However, write variation poses a major challenge in designing cache or memory subsystems with limited write endurance. Severe write variation can drastically reduce the product's lifetime, as a small fraction of memory cells exposed to high write traffic can render the entire cache or memory subsystem inoperative, even if most cells remain far from wear-out. By exploiting this vulnerability, attackers can create malicious applications that reportedly write on one or few memory locations,

resulting in early wear out. Consequently, using NVMs as last-level caches (LLCs) without optimization techniques is challenging.

This section briefly summarizes our three proposed techniques that address this issue, enhancing the lifetime and performance of NVM caches. Figure 1.3 highlights the three main contributions of this thesis: two-lifetime improvement techniques tailored for SLC NVM LLCs and one combined lifetime and performance enhancement method for MLC NVM LLCs. Detailed explanations and analyses of these techniques are presented in the subsequent chapters.

In this thesis, we analyze the lifetime improvement and write distribution (intraset variation) achieved by our proposed techniques, which aim to ensure uniform write distribution and prevent repeated writes to memory. A reduction in intra-set variation inherently improves write distribution and reduces the system's susceptibility to malicious repeated write attacks. Therefore, we do not explicitly discuss detailed mitigation strategies for such attacks.

Figure 1.3: Overview of Thesis Contributions

# 1.2.1 Write Aware Last Level Non-Volatile Caches (WALL-NVC)

WALL-NVC is a promising lifetime enhancement technique for SLC NVM LLCs. Unlike the state-of-the-art lifetime improvement techniques for SLC NVM caches [10] [11] [12] [13] [14], WALL-NVC focuses on the impact of the cache replacement policies on the cache lifetime and implements a customized replacement policy for SLC NVM caches. Conventional cache block replacement strategies, such as Least Recently Used (LRU), cause the cache to wear down faster, as some cache blocks are retrieved more frequently than others. The thesis discusses Write Aware Last Level Non-Volatile Cache (WALL-NVC) for extending the lifetime of NVM while executing applications with non-uniform writes and to safeguard against targeted malicious attacks by repeatedly writing to certain blocks as its first contribution.

WALL-NVC is a dual-stage wear-leveling approach, contrasting with most modern wear-leveling methods. Choosing a better victim block for cache replacement in NVMs is handled by a new LRU-CB replacement policy, which is the first stage. The second stage uses a conventional write distribution technique with LRU-CB to extend the NVM lifetime. WALL-NVC is a reactive approach that uses counters at various levels of memory hierarchy to activate the write distribution mechanism. The Chapter 4 discusses the detailed description and analysis of WALL-NVC.

### 1.2.2 Virtually Split Last Level Non-Volatile Cache

Most of the modern processors use private split cache architecture for L1 caches and shared unified design for the subsequent levels of caches. The data blocks are more frequently accessed for writes than the instruction blocks. When NVMs are utilised in L1 caches, D-cache ages out more quickly than I-cache. Experimental studies indicate that in an L1 split cache, the D-cache experiences an average of 472x more writes than the I-cache [15]. This significant write variation between I and D caches indicates a significant variance in write access between instruction and data blocks. As stated before, data and instructions are stored together in unified last-level caches. Compared to the number of write operations to the blocks that store instructions,

we observe that the write count of the blocks that store data is high. By virtually splitting unified LLC for wear-leveling, our proposed approach, ViSC (Virtually Split Cache), explores the write variance across the data and instruction blocks.

ViSC logically divides the set of n-way set associative cache into m instructions ways and m-n data ways. The m instruction ways are exclusive for instructions and remaining m-n are exclusive for data. To distribute the writes uniformly, the logical mapping of LLC blocks into instructions and data is modified periodically. After every fixed time epoch, the blocks which are currently reserved for instruction will act as data blocks in next time epoch. Similarly, blocks which are reserved for data in current time epoch will act as instruction blocks. ViSC operates in three variants. The most proactive is the base version, which uses a static reorganisation interval and initiates reorganisation regardless of write pattern. The reorganisation interval is dynamically selected in the other two variants, E-ViSC and P-ViSC, based on the application write pattern. Chapter 5 of the thesis discusses the working and experimental analysis in detail.

#### 1.2.3 Trace buffer Assisted Last Level Non-Volatile Cache

NVMs can be realized as SLC or MLC. MLC NVMs store two or more bits of data in each memory cell, in contrast to SLC NVMs, which can only store a single bit per memory cell. Despite having a much higher packing density than SLCs, MLC NVMs have short lifetime and large access time. MLC caches use 1.84x less space and 2.62x less leakage power than SLC caches for a given cache size. To improve the lifetime and performance of MLC LLCs the thesis proposes Trace buffer Assisted Non-volatile Memory Cache (TANC) as its third contribution, which utilizes a portion of the underutilized Embedded Trace Buffers (ETB) to reduce frequent writes to MLC NVM LLCs. ETBs are storage spaces available in modern processors for post-silicon validation but are left unused afterwards.

The LLC blocks which are frequently accessed for write operations are kept in ETB and all the read/write request to that particular block are serviced from ETB instead of LLC. When ETB is full, least recently written block replaced by writing back its contents to LLC. This reduces the number of writes to MLC NVM LLC,

which has less write endurance as most of the write operations are done on SRAM based ETB. Based on the selection of LLC blocks stored in ETB, TANC has different variants, and one variant addresses the thrashing effect of cache memories caused by poor temporal and spatial locality of applications. Chapter 6 discusses on TANC and its variants in detail.

### 1.3 Thesis Organization

The thesis is organized into seven chapters. The brief description of the subsequent chapters is given below.

- Chapter 2 discusses about the background details of various NVM technologies, their characteristic features and challenges. This chapter also summarizes different state of the art techniques for life time and performance improvement of SLC and MLC NVM caches.

- Chapter 3 discusses about the experimental setup used for analysis and comparison of the proposed techniques with other state of the art techniques. This chapter briefs about the simulator used for the experiment and benchmarks used for the analysis.

- Chapter 4 discusses about the first contribution of the thesis, WALL-NVC a technique to enhance the lifetime of SLC NVM LLCs. The chapter discuss about working of the proposed technique, experimental setup, result analysis and comparison with other state-of-the-art lifetime improvement techniques for NVMs.

- Chapter 5 gives a detailed analysis of second contribution of the thesis, ViSC and its variants. ViSC is lifetime enhancement technique for SLC NVM LLCs. ViSC is a low overhead lifetime enhancement technique compared to similar techniques. Results for various system configurations of the proposed techniques are also discussed in this chapter.

- Chapter 6 is on the third contribution of the thesis, TANC which a novel lifetime enhancement technique for NVM LLCs. Unlike previous contributions

#### 1.3. Thesis Organization

TANC is an enhancement technique customized for MLC NVMs. TANC is a low overhead technique as it utilizes unused resources for lifetime enhancement and the result analysis discussed in this chapter shows that the proposed technique improves the lifetime and performance of SLC NVMs.

• Chapter 7 concludes the thesis and discusses few future works and extensions that can be done based on the contributions of the thesis.

## Background

In this chapter, we explore the functioning of emerging memory technologies, including Resistive RAM (ReRAM) [5], Phase Change Memory (PCM) [4], and Spin Transfer Torque RAM (STT-RAM) [1] [3], along with the challenges associated with their implementation as caches. Additionally, we review existing literature that provides a detailed discussion on state-of-the-art lifetime improvement techniques for NVM caches.

### 2.1 Emerging Memory Technologies

Emerging memory technologies, including STT-RAM, PCM and ReRAM are at the forefront of research and development in the quest for faster, more efficient, and more reliable memory storage solutions. These technologies offer unique advantages and characteristics, making them suitable for various applications.

Spin-transfer torque is a phenomenon where the orientation of a magnetic layer within a magnetic tunnel junction or spin valve can be altered by a spin-polarized current. This phenomenon finds application in flipping the active elements in magnetic random-access memory, known as Spin-Transfer Torque Magnetic Random-Access

Memory (STT-RAM or STT-MRAM). STT-RAM offers non-volatility and minimal leakage power consumption, a significant advantage over charge-based memories like SRAM and DRAM.

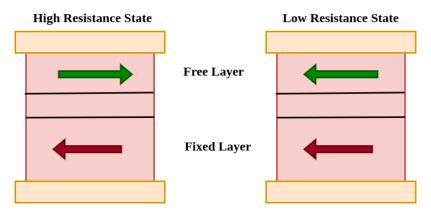

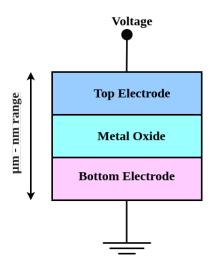

Figure 2.1: Schematic representation of an STT-RAM cell

As seen in Figure 2.1, STT-RAM, the second generation of Magneto Resistive RAM (MRAM) [2], uses the magnetic tunnel junction (MTJ) as a key component for bit information storage. An MTJ is made up of two ferromagnetic layers separated by a barrier layer. The fixed layer, also known as the reference layer, has a fixed magnetization direction, and the free layer, which can be changed by passing a spin-polarized current or an external magnetic field through the MTJ. When the reference layer and the free layer's magnetization directions are parallel, the MTJ displays a low-resistance state, signifying logical '0'. On the other hand, the MTJ assumes a high-resistance state when the two ferromagnetic layers' magnetization directions are anti-parallel representing logical '1'. STT-RAM also outperforms conventional MRAM in terms of lower power consumption and improved scalability, as MRAM relies on magnetic fields to switch the active elements.

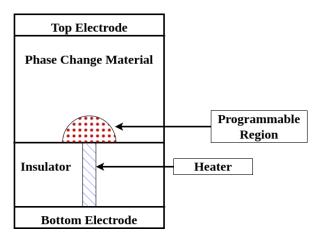

A typical Phase Change Memory (PCM) cell is shown in Figure 2.2. The crystalline phase of the phase change material has low resistivity, while the amorphous phase has high resistivity. This significant resistivity difference is exploited by PCM. In PCM, the states "set" and "reset" stand for low and high resistance conditions, respectively. The processing temperature of the metal interconnect layers is high enough to crystallize the phase-change material, resulting in an initial low-resistance crystalline state. During a reset, a large electrical current pulse is applied for a

brief period, melting and rapidly quenching the programming region of the PCM cell to cause it to transition to the amorphous phase. This process results in an amorphous, highly resistive region within the PCM cell, affecting the overall resistance between the top electrode contact and the bottom electrode contact. To set the PCM cell back to the crystalline phase, a moderate electrical current pulse is applied to anneal the programming region at a temperature between the crystallization and melting temperatures, ensuring sufficient time for crystallization. Reading the state of the programming region involves measuring the cell's resistance using a small electrical current that does not disturb the current state. A Resistive Random Access

Figure 2.2: Schematic representation of a PCM cell

Memory (ReRAM) [5] comprises a memory cell with a resistive switching mechanism, featuring a metal-insulator-metal structure. This structure involves an insulating layer positioned between two metal electrodes. The schematic view of an ReRAM cell are depicted in Figure 2.3. Applying an external voltage pulse across the ReRAM cell facilitates a transition from a high resistance state or OFF state (logic value '0') to a low resistance state or ON state (logic value '1'), and vice versa. Initially, ReRAM is in the high resistance state. To shift the device to low resistance state, a high-voltage pulse, SET voltage, is applied and it results in formation of conductive paths in the switching layer, resulting in the ReRAM cell transitioning low resistance state (SET process). Conversely, to switch the ReRAM cell from low to high resistance state, a voltage pulse, referred to as the RESET voltage, is applied, facilitating this transition and is denoted as the RESET process. For efficient data reading from the ReRAM

Figure 2.3: Schematic representation of a ReRAM cell

Table 2.1: Approximate values of device level properties for different memory technologies

|                              | SRAM        | DRAM          | PCM           | STT-RAM     | Re-RAM      |

|------------------------------|-------------|---------------|---------------|-------------|-------------|

| Cell size $(F^2)$            | 125-200     | 6-10          | 4-12          | 6-50        | 4-10        |

| Access granularity           | 64 B        | 64 B          | 64 B          | 64 B        | 64 B        |

| Read latency                 | 1-10 ns     | 10-20ns       | 50-100 ns     | 10 ns       | 10-50 ns    |

| Write latency                | 1-10 ns     | 10-20 ns      | 100-500 ns    | 10-100 ns   | 10-100 ns   |

| Endurance (number of writes) | $> 10^{15}$ | $> 10^{15}$   | $10^8 - 10^9$ | $> 10^{12}$ | $> 10^{11}$ |

| Standby power                | 60 nW       | Refresh power | 0             | 0           | 0           |

cell, a small read voltage, which does not disturb the current state of the cell, is applied. This voltage helps determine whether the cell is in a logic 0 or logic 1 state.

Approximate values of device level properties for different memory technologies are shown in Table 2.1. In comparison to SRAM and DRAM, emerging memory technologies exhibit significantly higher densities and comparable fast access times. Notably, non-volatile memory technologies possess zero standby power and are resistant to radiation-induced soft errors. Despite these advantages, the direct replacement of existing SRAM and DRAM technologies with the mentioned emerging memory technologies is challenging. For instance, SRAM and DRAM arrays are predominantly affected by leakage power. Conversely, while PCM or ReRAM arrays consume no leakage power when idle due to non-volatility, they demand considerably more energy during write operations. Consequently, exploring trade-offs in the utilization of diverse memory technologies at various hierarchy levels becomes a

crucial research area. Substituting SRAM-based on-chip cache with STT-RAM and PCM can enhance performance and decrease power consumption. The higher packing density of STT-RAM and PCM allows for a larger on-chip cache capacity, thereby reducing cache miss rates and improving overall performance. Zero standby leakage contributes to lowered power consumption. However, challenges associated with emerging memory technologies include the prolonged duration and increased energy consumption required for write operations. NVMs offer a more stable data storage mechanism than volatile SRAM and DRAM. Yet, directly replacing SRAM caches with PCM or STT-RAM caches may lead to performance drawbacks, particularly under high cache write intensity. Employing hybrid cache memory, buffers, and data compression becomes essential to mitigate the extended latency and elevated energy consumption in write operations for PCM or STT-RAM caches. Despite STT-RAM's higher density compared to SRAM, utilizing it directly as on-chip caches with frequent accesses proves impractical due to limited endurance. Wear-leveling is a technique widely used in NAND-flash memory, seeks to address write endurance limitations by evenly distributing write operations across storage cells, and this approach can also be applied to NVM caches and memory.

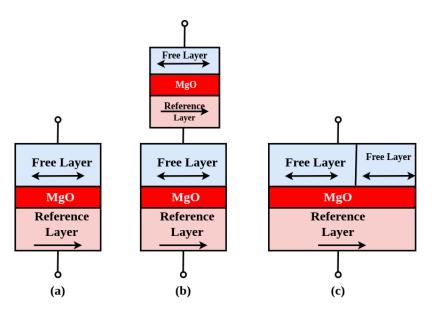

Among different NVM technologies, STT-RAM, with its superior write endurance and overall performance metrics, proves to be a more suitable choice for implementing last-level caches. In this thesis, we specifically adopt STT-RAM as our candidate to replace SRAM in cache memories, henceforth referring to NVM as STT-RAM. NVMs can be categorized as Single Level Cell (SLC) or Multi Level Cells (MLC). SLCs store one bit per memory cell, while MLCs can store two or more bits per memory cell. Figure 2.4 (a) illustrates the structure of SLC STT-RAM cell. An SLC STT-RAM cell consists of a Magnetic Tunneling Junction (MTJ) with free and reference ferromagnetic layers separated by an oxide layer, where the reference layer's magnetization direction is fixed and bits are stored by changing the free layer's magnetization direction. The MLC STT-RAM cell, can be either serial or parallel as shown in Figure 2.4 (b) and Figure 2.4 (c), respectively. In our work, we refer to MLC as serial MLC due to its superior performance and reliability compared to parallel MLCs. The serial MLC STT-RAM cell features two vertically stacked free

Figure 2.4: Schematic representation of (a) SLC (b) Serial MLC and (c) Parallel MLC STT-RAM cell

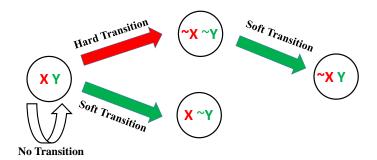

layers, while parallel MLC cells use a single MTJ with two independent free layers. In this context, the larger MTJ is termed a hard-bit with a high switching current, and the smaller MTJ, characterized by a lower switching current, is referred to as a soft-bit. Although MLC NVMs enhance data density, they exhibit higher lifetime, write energy, and latency compared to SLC. Soft-bit flipping is more straightforward than hard-bit flipping due to the smaller switching currents. Hard-bits, on the other hand, due to large switching currents, entail higher write energy and latency. The writes to hard-bits lead to the flipping of soft-bits, termed as write disturbance. Figure 2.5 illustrates how values are stored in the hard-bit (X) and the soft-bit (Y) of an MLC NVM cell, indicating possible state transitions and the retention of the current state. As illustrated in Figure 2.5, hard transitions cause the flipping of both hard- and soft-bits, while soft transitions only flip the soft-bit, leaving the hard bit unchanged. Therefore, to modify only the hard-bit, a two-step process is required: a hard transition followed by a soft transition. Cells can move from one state to another or retain its current state on following transitions, given below

- No transition: Current state of bits (hard and soft) are the same as new state (both bits retain current state)

- Soft transition: Change in current soft-bit state only whereas hard-bit retains

Figure 2.5: Hard and Soft-bit states during different transitions of a MLC STT-RAM cell

current state (small switching current)

- Hard transition: Change in hard-bit state. Soft-bit should retain/update its current state to updated hard-bit state (high switching current).

- Two-step transition: Change in a hard-bit only. Hard transition followed by soft transition.

The flipping of the soft-bit, denoted as Y to  $\sim$ Y, occurs in a single step as hard bits are unaffected by the small switching current. When a hard-bit transitions from X to  $\sim$ X, it leads to the simultaneous flipping of the associated soft-bit (from Y to  $\sim$ Y). However, due to this write disturbance, exclusive bit flips for hard-bits involve a two-step process. Initially, hard-bits undergo flipping using high switching currents, followed by the soft-bit being flipped back to its original state using a smaller switching current.

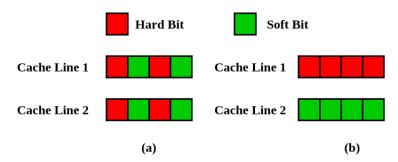

Since MLC NVMs have two different bits present in them, they can be configured to organize cache lines through in different approaches. Direct Mapping (DM) and Cell Split Mapping (CSM) as illustrated in Figure 2.6 are two popular stratagies for MLC NVM cache organizations. The organization of cache lines in the DM strategy involves a cache block comprising hard and soft bits, but it fails to leverage the faster accessibility of soft-bit cells. Conversely, in CSM, the hard bits of memory cells are grouped to form the hard-way, while all soft bits are grouped to form the soft-way.

CSM introduces variable latency for blocks based on their location. Read and write operations in the soft-way are streamlined into a single step. However, due to the potential for write disturbance, writing to the hard-way requires an initial read of the corresponding soft-way to safeguard its contents before completing the hard-way write. Experimental studies demonstrate that MLC based on CSM enhances system performance by 10.3% and reduces energy consumption by 26.0% [16] compared to conventional MLC STT-RAM and hence here after we consider CSM STT-RAM for our experiments and refer as MLC NVM.

Figure 2.6: 4 bit cache lines in (a) Direct Mapping (b) Cell Split Mapping

NVMs are prone to premature wear-out caused by non-uniform write patterns and repeated write attacks [17] [18] due to the limited write endurance. Numerous state-of-the-art techniques have been developed to enhance the lifetime and performance of SLC and MLC NVMs. Next section delves into a detailed discussion of such advancements. While the improvement in the lifetime of SLC NVMs has been extensively explored, MLC NVMs face challenges due to their structural peculiarities. Implementing conventional SLC wear-leveling algorithms in MLC is considered challenging and not cost-effective.

### 2.2 Related Works

This section explores various techniques aimed at enhancing the lifetime and performance of SLC and MLC NVMs. Researchers across the globe have proposed diverse strategies to tackle the challenges associated with improving the endurance of NVM LLCs. These approaches include wear-leveling techniques [11] [13] [12] [14] [6], write reduction methods [19] [20], hybrid cache architectures [21] [10], and data

compression schemes [22]. Each of these methods addresses specific aspects of write variations and performance bottlenecks inherent in NVMs. In this section, we will delve into some of the most relevant and impactful works in detail, highlighting their contributions and limitations.

J. Wang et al. proposed  $i^2wap[6]$ , a technique which leverages two global counters and registers.  $i^2wap$  incorporates swap-shift, a wear-leveling strategy minimizing cache inter-set write variations, and Probabilistic Set Line Flush (PoLF), a novel approach for mitigating intra-set write variations. Key idea behind PoLF is that the frequent access to hot data blocks, which remains unchanged in traditional replacement policies, causes write variations. PoLF probabilistically flushes hot data to optimize write distribution. In case of a cache write hit, instead of writing directly to the hit data block, the new data is placed in the write-back buffer, marking the cache line as invalid. Consequently, other cold data can replace the block containing the hot data, allowing the relocation of hot data to other areas. Sparsh Mittal et al. proposed EqualWrites [12] and EqualChance [11] techniques to reduce intra-set variation and improve the lifetime of non-volatile memory caches. EqualWrites identifies substantial intra-set write variation when the difference between the number of writes to two blocks in a cache set exceeds a threshold. By swapping data items in these blocks, intra-set write variation is reduced, leading to a better distribution of writes and enhanced cache life. The EqualChance mechanism periodically changes the block locations of data to distribute writes more uniformly across cache lines. To achieve this, it uses counters to track the number of writes for each set. After a certain threshold of writes is reached, hot (frequently written) data is swapped with cold (infrequently written) data. The swap candidates may either be invalid blocks, a process termed I-shifting, or clean blocks, referred to as C-shifting. Dirty blocks are excluded from the swapping process since they are likely to be frequently written and would not effectively reduce wear. Another state-of-the-art approach for extending the lifetime of NVM caches is the use of periodically interchangeable write-restricted window. Techniques like Static Window Write Restriction (SWWR) [14], Dynamic-Window Write Restriction (DWWR), and Dynamic Way Aware Write Restriction (DWAWR) [13] fall under this category. SWWR divides the cache into logical windows, treating one as a write-restricted window during each interval, with writes redirected to other windows. The core concept of DWWR involves dividing the cache into m equally sized windows and using a different window during each predefined execution interval. Unlike SWWR, where the write-restricted window is chosen in a roundrobin manner, DWWR selects the window based on a counter associated with each window. This counter tracks the number of writes during the previous interval (i.e., from the upper-level cache to the last-level cache). At the start of each interval, the window with the highest number of writes is designated as the write-restricted (or read-only) window. Once the interval ends, the next write-restricted window is determined based on the counter values, and this process continues throughout execution. To avoid selecting the same window consecutively, the counter for the current write-restricted window is reset at the end of each interval. DWAWR selects heavily written ways instead of fixed windows as write-restricted for a given interval, providing effective wear-leveling. As previously discussed, the MLC NVM exhibits a shorter lifetime compared to SLC due to write disturbance. To mitigate the impact of write disturbance on soft-ways, a mechanism is required to safeguard data in soft-ways during hard-way writes. One simplistic solution is the Immediate Restore Scheme (IRS), in which the corresponding soft-way is read and rewritten after the completion of the hard-way write operation to ensure data consistency. The Adaptive Restoration Scheme [23] for write disturbance and read disturbance comprises two schemes for addressing write and read disturbances in MLC NVMs. To tackle write disturbances, this technique overwrites the soft-bit lines, which are less likely to be read, accumulating potential writes to address read disturbance. The soft-bit line is restored during eviction from the higher cache level. Both approaches demonstrate performance enhancement and substantial energy savings for MLC STT-RAM caches. The self-adaptive wear-leveling technique, designed for MLC NVM, achieves wear leveling by balancing writes across memory cells using two mapping tables; a global directory and an on-chip SRAM cache that maintains recently accessed mappings.

Another strategy for minimizing read disturbances is the restore-free mode [24], involving two-step read/write operations for frequently used hard-ways in MLC STT-RAM cache. This technique allows the logical turning off of specific hard/soft

domains in an MLC by fixing their data to "0" or "1". In the restore-free mode, the corresponding soft-way of the frequently used hard-way is deactivated after invalidation, and its data is written to a lower-level memory. Although eliminating write disturbance restorations streamlines hard-way writes into a one-step process and reduces energy consumption, the energy required for hard-way writing remains higher than for soft-way writing.

The technique of Alternative Encoding [22] aims to reduce two-step transitions in MLC STT-RAM cache. It employs two 3-bit codes for each 2-bit data, providing flexibility to eliminate two-step transitions. However, this encoding method results in a larger data size, improving the lifetime of the MLC STT-RAM cache. Despite sacrificing some data density, the data density of the alternating encoding-based MLC STT-RAM cache still surpasses that of the SLC STT-RAM cache. P. Saraf et al. [25] proposed replacement policies like the Refresh Aware Replacement Policy (RFR) to improve the lifetime and performance of STT-RAM caches. The authors focus on reducing the maximum number of writes, global write variation, and the average number of writes to enhance the endurance of write-optimized STT-RAM caches. Write-optimized STT-RAM refers to a configuration of STT-RAM designed to reduce its inherently high write latency by lowering the thermal barrier of its MTJ cells. The thermal barrier is a measure influenced by the physical and material properties of the MTJ, such as planar area, magnetic parameters, and free layer thickness. Reducing the thermal barrier decreases the switching current and the write pulse width (the duration for applying the switching current), resulting in faster write operations. However, reducing the thermal barrier also leads to a shorter retention time, the duration for which data can be reliably stored in an STT-RAM cell without a random bit flip. Refresh mechanisms are employed to mitigate the shorter retention time in write-optimized STT-RAM. Blocks that remain in the cache beyond their retention period are rewritten to prevent data loss, effectively maintaining reliability. Refresh-aware cache replacement policies also prioritize evicting blocks about to expire over recently refreshed blocks to balance performance and endurance. The techniques for enhancing the lifetime of NVM caches discussed thus far can be categorized into reactive and proactive approaches. Reactive methods use cache monitoring tools,

such as counters, to trigger specific actions once predefined conditions (e.g., reaching a threshold value) are met. On the other hand, proactive techniques continuously maintain enhancement mechanisms active, regardless of the application's behavior or execution time window. Many of the previously mentioned approaches rely heavily on counters or additional circuitry, leading to increased overhead. Upon further analysis of these methods,  $i^2wap$  [6] is found to have a drawback: it may invalidate the Most Recently Used (MRU) blocks, causing more accesses to the main memory. EqualChance swaps write-intensive blocks within a cache set with invalid or clean blocks based on a write counter threshold, but this requires more write counters, contributing to greater area and power overhead. SWWR uses a round-robin window selection process, which does not consider the write counts of other windows within the cache set, potentially allowing heavily written windows (or ways) to accumulate in the cache bank and negatively affecting cache lifetime. DWWR lacks consideration for heavily written ways that may exist in lightly written windows, meaning that even if a window has a low write count, it could still contain some highly written ways that are neglected. Lastly, RFR, while effective for write-optimized caches, is less effective for unoptimized caches. These shortcomings prompted us to explore techniques that can improve both the lifetime and performance of NVM caches with minimal overhead. This thesis proposes the following approaches for SLC and MLC NVM LLCs:

- WALL-NVC, a reactive technique utilizing a custom cache replacement algorithm designed for SLC NVM caches to enhance their lifespan.

- ViSC, a proactive technique that involves logically splitting the SLC NVM-based unified LLC. It also introduces variants E-ViSC and P-ViSC, falling into the hybrid category, incorporating features from both proactive and reactive approaches.

- TANC, a technique focused on enhancing the lifetime and reducing the write latency of MLC-based NVM caches.

We discuss these techniques in detail in the subsequent chapters. Table 2.2 compares the key ideas of selected techniques discussed in this section along with the

proposed techniques. Detailed analysis is given in coming chapters.

Table 2.2: Overview of proposed techniques and state-of-the-art approaches

|              | Key feature                                                           | Supports SLC NVM      | Supports MLC NVM |

|--------------|-----------------------------------------------------------------------|-----------------------|------------------|

| $i^2wap$     | Probabilistic line flushing                                           | Yes                   | No               |

| EqualWrites  | Write distribution using counters                                     | Yes                   | No               |

| EqualChance  | Write distribution using counters                                     | Yes                   | No               |

| DWWR         | Write restriction using set partitioning (windows)                    | Yes                   | No               |

| Restore Free | Two step write reduction in MLC NVM caches                            | No                    | Yes              |

| WALL-NVC     | Write distribution using counter with NVM friendly replacement policy | Yes                   | No               |

| ViSC         | Write distribution using logical partitioning                         | Yes                   | No               |

| TANC         | Write reduction using Embedded trace buffer                           | Yes (Can be modified) | Yes              |

Снартек

3

# Experimental Setup

This chapter discusses about the overview of experimental setup used for analyzing the proposed techniques. Detailed experimental details for each contributions are given in corresponding chapters.

# 3.1 Adopted simulation environment

Simulators are software tools that mimic the operation of real-world systems or processes in a controlled and reproducible environment. They are used for testing, analysis, training, and research without the risks or costs associated with real-world implementation. Simulators allow architects and engineers to test new designs and configurations before physical implementation, identifying potential issues and optimizing performance. They enable detailed performance analysis of various architectural components under different workloads, such as CPUs, memory hierarchies, and interconnects. Organizations can reduce the costs and risks associated with building and testing physical prototypes by simulating designs. They help to verify that architectural changes or enhancements meet the required specifications and performance targets.

We employ the gem5 simulator [26] to analyze and implement the proposed techniques. Widely embraced in both academic and industrial circles, the gem5 simulator originated from the merger of the m5 simulator [27] at the University of Michigan and the GEMS simulator [28] from the University of Wisconsin. The gem5 simulator is highly modular, allowing users to customize and extend the simulator to meet specific research needs. It supports multiple CPU models, memory systems, and interconnects. The gem5 provides detailed and accurate models of modern processor architectures, including in-order and out-of-order cores, detailed memory systems, and various interconnects. It supports multiple instruction set architectures (ISAs), including ALPHA, x86, ARM, MIPS, RISC-V, and SPARC, making it versatile for different research scenarios. The gem5 simulator can simulate entire systems, including operating systems and full applications, providing a comprehensive view of system behaviour. Users can easily configure and modify various architectural parameters, enabling experimentation with different design choices and performance trade-offs. It can be integrated with other simulation and analysis tools, enhancing its capability for comprehensive architectural studies.

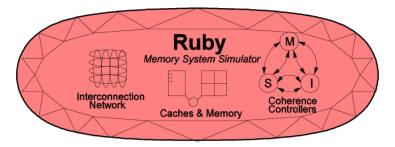

In our experiments, we utilize Ruby to model memory. Ruby, the memory system simulator within gem5, is a modular framework designed to model and simulate detailed memory hierarchies in modern computer systems. Ruby's advantage lies in its ability to keep coherence protocol specifications distinct from replacement policies and cache index mapping, allowing separate specification of network topology from implementation. Additionally, Ruby is highly configurable in nature and facilitates rapid prototyping. As shown in Figure 3.1, Ruby integrates three key components:

Figure 3.1: High-level view of the main components in Ruby [Image source: gem5 documentation (https://www.gem5.org)]

the interconnection network, which facilitates communication between processors, caches, and memory controllers using various topologies like mesh or bus; caches and memory, representing the hierarchical structure of caches (L1, L2, L3) and main memory, allowing detailed analysis of cache behaviours such as hits, misses, and replacement policies; and coherence controllers, which enforce consistency across caches using protocols like MSI (Modified, Shared, Invalid) or more advanced ones like MESI or MOESI. The coherence controllers ensure proper transitions between states (e.g., Modified, Shared, Invalid), while the interconnection network connects all components, enabling seamless data flow. The cache coherence in our setup is maintained using the MESI Two Level protocol [29], which features a two-level cache hierarchy with private L1 cache and shared L2 cache. In this arrangement, L1 and L2 maintain inclusion between them. At a higher level, the MESI Two Level protocol encompasses four stable states: M, E, S, and I. A block in the M state indicates that it is writable and has exclusive permission, having been dirtied as the only valid on-chip copy. The E state represents a cache block with exclusive permission (writable) but not yet written. S state signifies that the cache block is only readable, with multiple copies possibly existing in various private caches and the shared cache. The I state denotes that the cache block is invalid.

### 3.2 Benchmark Programs

For experimenting with our proposed architectures across different application categories, we utilize the SPEC CPU2006 benchmark suite [30]. The SPEC CPU2006 benchmarks, developed by the Standard Performance Evaluation Corporation (SPEC), are widely used in the evaluation of computer systems' CPU performance. SPEC CPU2006 includes diverse benchmarks designed to represent a wide range of applications. This ensures that the benchmarks are not biased toward any particular type of workload. The benchmarks are derived from actual applications and scientific computations, providing a realistic performance measure. The benchmarks are designed to be complex and compute-intensive, making them representative of real-world scenarios that require significant computational power. SPEC CPU2006 benchmarks

can be compiled and run on various computer architectures and operating systems, facilitating performance comparisons across different systems.

Table 3.1: Selected SPEC CPU2006 Benchmarks with arconyms and category

| Name Description                             |                                              | WPKI | MPKI |

|----------------------------------------------|----------------------------------------------|------|------|

| astar (As)                                   | astar (As) Path finding algorithms           |      | Mid  |

| bzip2 (Bz)                                   | Compression                                  | Mid  | High |

| calculix (Ca)                                | culix (Ca) Structural Mechanics              |      | Low  |

| gromacs (Gr)                                 | gromacs (Gr) Biochemistry/Molecular dynamics |      | Low  |

| h264ref (H2)                                 | h264ref (H2) Video compression               |      | Low  |

| hmmer (Hm)                                   | hmmer (Hm) Search gene sequence              |      | Low  |

| lbm (Lb)                                     | lbm (Lb) Fluid dynamics                      |      | High |

| leslie3d (Ls)                                | leslie3d (Ls) Fluid dynamics                 |      | Mid  |

| libquantum (Lq)                              | Physics: Quantum computing                   | Mid  | High |

| mcf (Mc)                                     | Combinatorial optimization                   | High | High |

| milc (Mi)                                    | Physics: Quantum chromodynamics              | Mid  | High |