### INDIAN INSTITUTE OF TECHNOLOGY GUWAHATI

# Energy and Thermal Management of CMPs by Dynamic Cache Reconfiguration

# by Shounak Chakraborty

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the

Department of Computer Science and Engineering

Under the supervision of Prof. Hemangee K. Kapoor

February 2018

# **Declaration of Authorship**

- I, Shounak Chakraborty, hereby confirm that:

- The work contained in this thesis is original and has been done by myself under the general supervision of my supervisor.

- This work has not been submitted to any other Institute for any degree or diploma.

- Whenever I have used materials (data, theoretical analysis, results) from other sources, I have given due credit to the authors/researchers by citing them in the text of the thesis and giving their details in the reference.

- Whenever I have quoted from the work of others, the source is always given.

#### Shounak Chakraborty

Research Scholar, Department of CSE, Indian Institute of Technology Guwahati, Guwahati, Assam, INDIA 781039, c.shounak@iitg.ernet.in, shou46@gmail.com

Date: February 28, 2018 Place: IIT Guwahati

## Certificate

This is to certify that the thesis entitled "Energy and Thermal Management of CMPs by Dynamic Cache Reconfiguration" being submitted by Mr. Shounak Chakraborty to the department of *Computer science and Engineering, Indian Institute of Technology Guwahati*, is a record of bonafide research work under my supervision and is worthy of consideration for the award of the degree of Doctor of Philosophy of the Institute.

#### Prof. Hemangee K. Kapoor

Department of CSE, Indian Institute of Technology Guwahati, Guwahati, Assam, INDIA 781039, hemangee@iitg.ernet.in

Date: February 28, 2018 Place: IIT Guwahati

### Dedicated to

Late Shyamapada Adhikary (my maternal grandfather)

and

Late Nandan Adhikary & Late Gautam Adhikary (both of my maternal uncles)

and

my loving parents & all of my teachers.

## Acknowledgements

It is great pleasure for me to thank all the people whose instinct supports and encouraging attitudes always boost me up to engineer my initial research career. First and foremost, I thank to my supervisor Prof. Hemangee K. Kapoor for her guidance, patience and encouragement over the last five and half years. Her unwavering enthusiasm for Computer Architecture kept me constantly engaged with my research work. Needless to say, the journey of PhD is a small demonstration of our life, which has uncountable number of ups and downs. The strong association of five and half years with her taught me about handling different situations with a gentle smile. The plethora of wonderful discussions with her helped me a lot to understand how to visualise something from a philosopher's point of view.

I take the opportunity to thank my Doctoral Committee members: Prof. Diganta Goswami, Prof. Purandar Bhaduri and Dr. Arnab Sarkar for their fruitful and constructive suggestions, which help me enough to shape up my final thesis. Sincerely, I would also like to thank Prof. Kalpesh Kapoor and Dr. Arnab Sarkar for numerous academic/non-academic suggestions. Discussions with them are always fun irrespective of the topics. Furthermore, my sincere thank to Prof. S. V. Rao, the Head of the Department of Computer Science and Engineering and other faculty members for their constant supports and helps.

I sincerely thank to Mr. Souvik Chowdhury, Mr. Raktajit Pathak, Mr. Nanu Alan Kachari, Mr. Bhriguraj Borah and all other institute's staffs who helped me at different times during my stay at IIT Guwahati. I must mention and thank to the Student Affairs section for providing on-campus hostel facility. I am conveying my appreciation to all the hostel and canteen staffs, security guards, housekeeping staffs who made my life smooth at the campus.

Life is incomplete without a set of good friends. I am fortunate enough to have such a good set of friends during PhD who constantly push me to enhance my creative thinking. I really feel privileged to have the company of Mandar, Suman, Abhradeep, Mitali, Arindam, Pramit, Krishnanjan, Srimoy, Niladri, Mriganka, Jinat, Gourhari, Gundappa, Atanu, Bihan, Susmita, Anwesika, Dr. Shuvendu, Dr. Sibaji, Dr. Dishari, Karnika, Arya, Ramyani, Soheni, Arunangshu, Dr. Himadri, Omkar, Deepanjan, Debojit, Abhinandan, Arunabha, Soumi and Sayan. Uncountable number of discussions especially reagrding different forms of performing arts along with our own creations really added some special flavours to my PhD life, which are inexpressible. I am also thankful to my Tabla guru Mr. Dhriti Gobinda Dutta for his unforgettable inspirational lectures. During my PhD, I have also spent some joyous moments with my fellow research scholars like Biswajit, Dr. Debanjan, Dr. Pradeep, Mrityunjay, Rahul, Basant, Piyoosh, Rajesh, Monojit, Shilpa, Sandeep, Awnish, Durgesh, Akash, Ranajit, Amit, Shubhrendu, Dr. Suddhashil, Dr. Suchetana, Dr. Ashok, Dr. Niladri, Dr. Mayank, Satish, Dr. Nilkanta, Subrata, Anasua, Aparajita, Abhijit, Shrestha, Ujjwal, Hema, Sumita, Sanjukta and many more. I must mention the name of Dr. Sandip Chakraborty, a iconic character in my life, whose constant support during initial stages of my PhD is unforgettable. I am also thankful to Mr. Lalatendu Behera for adding some special colours to my PhD life.

During my PhD, I got the opportunity to work with Dr. Shirshendu Das, Dipika Deb, Sukarn Agarwal, Palash Das, Sheel Sindhu Manohar, Arijit Nath, Khushboo Rani, T. Susma Devi, Major Alankar Umdekar, Prateek Halwe, Gibran Iqbal and Arpit Agarwal. Sharing of knowledge with them, during countless number of technical/non-technical discussions were amazing and simply helped me to carry out my research work. I would also like to convey my respects and special thanks to Mrs. Manjari Saha, Mr. Avijit Bose, Prof. Ranjani Parthasarathi, Mr. Arnab Biswas and Mr. Biswajit Sanyal. I am also thankful to all the anonimous reviewers of my papers & thesis and my friends inside & outside the IIT Guwahati.

Finally, I would like to share a few words about my family. Their constant support along with strong motivations always kept me focused to my research work. I am extremely thankful to all of my beloved family members who have channelised enough mental strength and encouragement during all ups and downs of my PhD life. I cannot express enough thanks to my parents, the two most important persons in my life, who show me the correct path with the onset of my life. Instinctively they encouraged me in each step of my life with due respect to my every thoughts and decisions. Lastly, towards completion, I should express my thanks to all of those people who demoralised/discouraged/refused me to help at different moments/stages of my life, as it indoctrinated me about taking something as a challenge with sound cultivation of my own thoughts.

### Abstract

Ever increasing demand of processing speed and parallelism, along with the modern shrunk transistors, motivates the architects to increase the number of cores on a single chip leading to Chip Multi-Processors (CMPs). To commensurate the data demand of these high number of cores, large on-chip Last Level Caches (LLCs) are integrated. After studying a plethora of prior works, it has been concluded that, LLCs play a vital role in maintaining system performance by accumulating more data on-chip. But large sized LLCs are accounted for their significant leakage energy consumption, which has a circular dependency on the effective temperature of the chip-circuitry. In addition to curtailing the circuit's reliability, this increased chip temperature (caused due to heavy power consumption) has enough potential to damage the on-chip circuitry permanently, and to exacerbate the battery life in embedded systems.

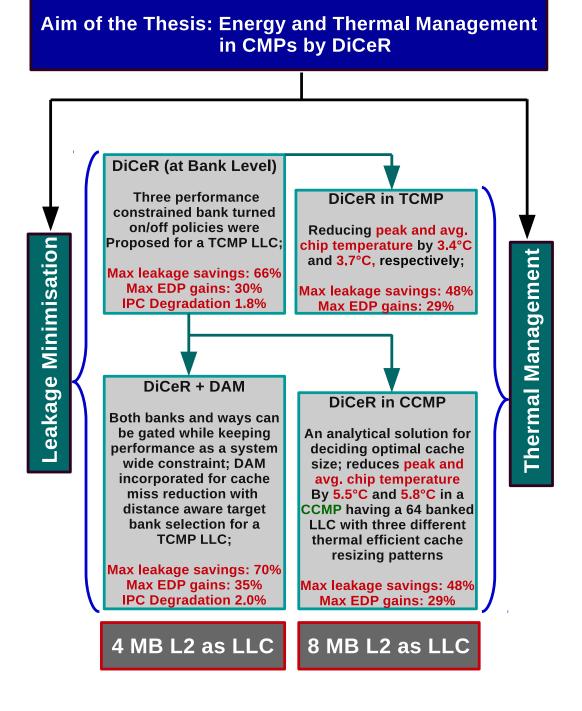

Towards leakage minimised on-chip cache design, with due consideration to the Locality of Reference, we propose a set of performance constrained Dynamic Cache Resizing techniques to reduce leakage in LLCs. The resizing is done by turning off/on some cache banks which can be implemented by power gating at circuit level. The cache resizing decision is triggered based upon the dynamic (cache) usage and change in system performance. We get 65% savings in leakage energy consumption. In the next contribution, apart from bank level granularity, we proposed cache resizing at way-level granularity, where performance degradation is handled by incorporating DAM (Dynamic Associativity Management) techniques. In this policy, we obtain 70% improvement in the leakage energy. Both of these techniques outperform a prior state preserving leakage reduction technique called, Drowsy cache; both in terms of leakage savings and EDP gains. All of these techniques are evaluated for tiled CMP having a multi-banked shared L2 cache as its on-chip LLC.

From the thermal efficiency perspective, it has been noticed that, larger caches fabricated in smaller technology nodes are the potential candidates for generating hotspots similar to the CPU cores. The increased power density at heavily used cache zones can heated them up faster, whereas the lightly used cache portions unnecessarily consume high leakage, which has a circular dependency with chip temperature. To mitigate these issues, our proposal selectively turns off LLC banks to reduce temperature by reducing their power consumption. Moreover, these turned off cache portions are utilised as on-chip thermal buffers that reduce effective chip temperature. The proposal is evaluated for tiled CMP architecture as well as CMPs having large multi-banked centralised LLCs. These approaches reduce average chip temperature by around 4°C and 6°C, respectively, for both architectures. The results are also compared with DVFS methods.

The thesis has thus demonstrated that, large LLCs on-chip need resizing for optimal power management and they can also assist in controlling chip temperature.

# Contents

\_

| Declar  | ation o | of Authorship                   |  |   | iii          |

|---------|---------|---------------------------------|--|---|--------------|

| Certifi | cate    |                                 |  |   | $\mathbf{v}$ |

| Ackno   | wledge  | ements                          |  |   | ix           |

| Abstra  | act     |                                 |  |   | xi           |

| List of | f Figur | es                              |  |   | xix          |

| List of | f Table | 25                              |  | X | xiii         |

| Abbre   | viatior | 18                              |  | 3 | xv           |

| 1 Int   | roduct  | ion                             |  |   | 1            |

| 1.1     | Mode    | rn Chip Multi-Processors (CMPs) |  |   | 3            |

|         | 1.1.1   | Components in CMPs              |  |   | 4            |

|         |         | 1.1.1.1 On-Chip Caches          |  |   | 5            |

|         |         | 1.1.1.2 Placement of LLCs       |  |   | 7            |

|         |         | Tiled CMP (TCMP)                |  |   | 7            |

|         |         | CMP with Centralised LLC (CCMP) |  |   | 7            |

| 1.2     | Power   | r Consumption in CMPs           |  |   | 8            |

|         | 1.2.1   | Dynamic Power                   |  |   | 8            |

|         | 1.2.2   | Static Power                    |  |   | 9            |

|         | 1.2.3   | Short-Circuit Power             |  |   | 10           |

| 1.3     | Thern   | nal Issues in CMPs              |  |   | 11           |

|         | 1.3.1   | Thermal Characteristics         |  |   | 11           |

|         | 1.3.2   | Mitigations-at a glance         |  |   | 12           |

| 1.4     |         | e based Mitigations             |  |   | 14           |

|         | 1.4.1   | Leakage Minimisation            |  |   | 14           |

|         | 1.4.2   | Controlling Temperature         |  |   | 15           |

|         | 1.4.3   | Objectives of this work         |  |   | 15           |

| 1.5     | Motiv   | vations                         |  |   | 16           |

|          | 1.6 | Princi | pal Contributions                                                                                                                              | 17 |

|----------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          |     | 1.6.1  | DiCeR at Cache Bank Level                                                                                                                      | 17 |

|          |     | 1.6.2  | DiCeR in combination with DAM technique                                                                                                        | 18 |

|          |     | 1.6.3  | DiCeR for temperature control in TCMP                                                                                                          | 19 |

|          |     | 1.6.4  | DiCeR for temperature control in CCMP                                                                                                          | 20 |

|          | 1.7 | Summ   | ary                                                                                                                                            | 21 |

|          | 1.8 | Organ  | isation of Thesis                                                                                                                              | 22 |

| <b>2</b> | Bac | kgrou  | nd                                                                                                                                             | 25 |

|          | 2.1 | Access | s Patterns of Shared LLCs                                                                                                                      | 25 |

|          |     | 2.1.1  | Bank Level Granularity                                                                                                                         | 26 |

|          |     | 2.1.2  | Set Level Granularity                                                                                                                          | 27 |

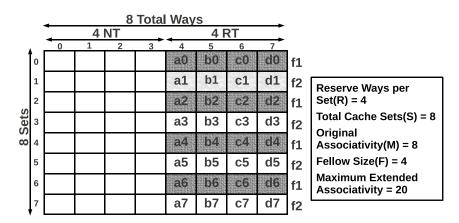

|          |     | 2.1.3  | Dynamic Associativity Management (DAM)                                                                                                         | 28 |

|          |     |        | 2.1.3.1 CMP-SVR                                                                                                                                | 28 |

|          |     | 2.1.4  | Violation in Locality of Reference                                                                                                             | 30 |

|          | 2.2 | Cache  | Energy Modeling                                                                                                                                | 32 |

|          |     | 2.2.1  | Dynamic and Leakage Energy                                                                                                                     | 32 |

|          |     | 2.2.2  | Channel Length, Temperature and Leakage                                                                                                        | 34 |

|          | 2.3 | Reduc  | ing Cache Leakage Consumption                                                                                                                  | 36 |

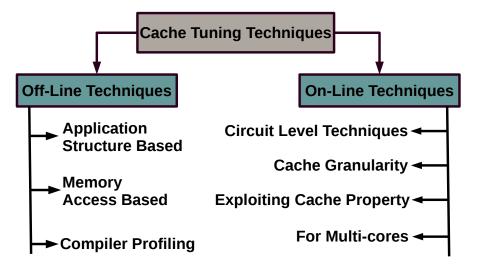

|          |     | 2.3.1  | Off-Line Techniques                                                                                                                            | 37 |

|          |     |        | 2.3.1.1 Application Structure Based                                                                                                            | 38 |

|          |     |        | 2.3.1.2 Memory Access Trace driven                                                                                                             | 39 |

|          |     |        | 2.3.1.3 Compiler Profiling/OS level approaches                                                                                                 | 40 |

|          |     | 2.3.2  | On-Line Techniques                                                                                                                             | 41 |

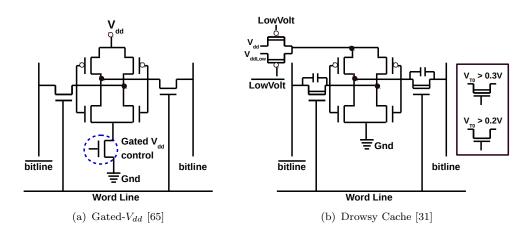

|          |     |        | 2.3.2.1 Circuit Level/Micro-architecture Based techniques                                                                                      | 41 |

|          |     |        | 2.3.2.2 Optimisation at different Cache Granularity                                                                                            | 43 |

|          |     |        | 2.3.2.3 Exploitation of different Cache Property                                                                                               | 45 |

|          |     |        | 2.3.2.4 Techniques for Multi-Cores/Multi-Processors                                                                                            | 46 |

|          |     |        | 2.3.2.5 Frequency of Cache Reconfiguration                                                                                                     | 47 |

|          | 2.4 | Therm  | nal Management in CMPs                                                                                                                         | 49 |

|          |     | 2.4.1  | Core Level Management                                                                                                                          | 50 |

|          |     | 2.4.2  | Cache Based Policies                                                                                                                           | 52 |

|          | 2.5 | Summ   | ary                                                                                                                                            | 54 |

| 3        | Sim | ulatio | n Framework                                                                                                                                    | 57 |

|          | 3.1 | Comp   | uter Architecture Simulators                                                                                                                   | 58 |

|          |     | 3.1.1  | Simics                                                                                                                                         | 59 |

|          |     |        | 3.1.1.1 Limitations of Simics                                                                                                                  | 60 |

|          |     | 3.1.2  | GEMS: An Overview                                                                                                                              | 61 |

|          |     |        | 3.1.2.1 CMP Architectures Supported by GEMS                                                                                                    | 62 |

|          |     |        | 3.1.2.2 Result Analysis $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                         | 63 |

|          |     | 3.1.3  | CACTI                                                                                                                                          | 64 |

|          |     | 3.1.4  | McPAT                                                                                                                                          | 65 |

|          |     | 3.1.5  | $HotSpot \ldots \ldots$ | 65 |

|          |     |        |                                                                                                                                                |    |

|          | 3.2 | Benchm   | narks                                                                                      | 66        |

|----------|-----|----------|--------------------------------------------------------------------------------------------|-----------|

|          |     | 3.2.1    | Parsec Benchmark Suite                                                                     | 68        |

|          |     |          | 3.2.1.1 Blackscholes                                                                       | 68        |

|          |     |          | 3.2.1.2 Bodytrack                                                                          | 69        |

|          |     |          | $3.2.1.3  \text{Facesim}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 69        |

|          |     |          | $3.2.1.4  \text{Ferret}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $  | 69        |

|          |     |          | 3.2.1.5 Fluidanimate $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                 | 70        |

|          |     |          | 3.2.1.6 Frequine                                                                           | 70        |

|          |     |          | 3.2.1.7 Swaptions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$  | 70        |

|          |     |          | 3.2.1.8 Vips                                                                               |           |

|          |     |          | 3.2.1.9 X264                                                                               |           |

|          | 3.3 |          | tion Methodologies                                                                         |           |

|          |     |          | Multi-threaded vs. Multi-programmed Benchmarks                                             |           |

|          |     |          | Used Benchmark Applications                                                                |           |

|          |     |          | Executing Benchmarks                                                                       |           |

|          |     |          | Comparing Different CMP Architectures                                                      |           |

|          |     | 3.3.5    | Our Architectural Models                                                                   | 75        |

| 1        | Sta | tia Enor | www. Reduction by Donformance Linked Dynamic Ca                                            | aha       |

| 4        |     | izing (I | rgy Reduction by Performance Linked Dynamic Ca                                             | cne<br>77 |

|          | 4.1 | - 、      | $\mathbf{r}$                                                                               |           |

|          | 4.2 |          | ed Energy Saving Policy                                                                    |           |

|          | 4.4 | -        | Book Keeping and Future Requests                                                           |           |

|          |     | 1.2.1    | Storage Overhead for Source Bank Tracking                                                  |           |

|          |     | 4.2.2    | Constraints to maintain                                                                    |           |

|          | 4.3 |          | nental Evaluation                                                                          |           |

|          | 1.0 |          | Experimental Setup                                                                         |           |

|          | 4.4 |          | and Analysis                                                                               |           |

|          |     |          | Comparison with baseline architecture                                                      |           |

|          |     |          | Comparison with BSP and Drowsy [1]                                                         |           |

|          |     |          | Analysis of power savings by varying the IPC constraint                                    |           |

|          |     |          | Analysis of proposed policy on a larger cache                                              |           |

|          |     |          | Summary                                                                                    |           |

|          | 4.5 |          | sion                                                                                       |           |

|          |     |          |                                                                                            |           |

| <b>5</b> |     | -        | tatic Energy Consumption in Way Sharing LLCs: D                                            |           |

|          |     | h DAM    |                                                                                            | 107       |

|          | 5.1 |          | ction                                                                                      |           |

|          | 5.2 |          | y Latency in DiCeR                                                                         |           |

|          | 5.3 | -        | ed Energy Saving Policy                                                                    |           |

|          |     |          | BSP vs. BSP_SVR: A Comparative Analysis                                                    |           |

|          |     |          | DiCeR with DAM at Multiple Granularities                                                   |           |

|          |     |          | 5.3.2.1 Effects of Way Shutdown on CMP-SVR                                                 |           |

|          | 5.4 | -        | nental Evaluation                                                                          |           |

|          |     | 5.4.1    | Results and Analysis                                                                       | 120       |

|          |     |          |                                                                                            |           |

|   |     | Gains in EDP                                        | . 120 |

|---|-----|-----------------------------------------------------|-------|

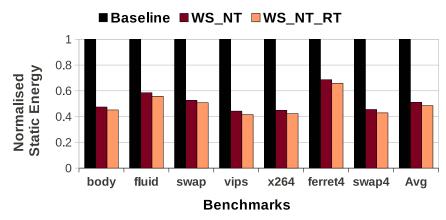

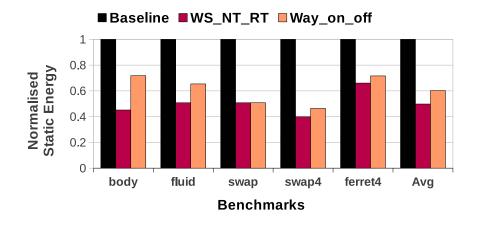

|   |     | Static Energy savings                               | . 120 |

|   |     | Effect on Higher Associative Caches                 | . 121 |

|   |     | Effect on Smaller Sized Cache                       | . 122 |

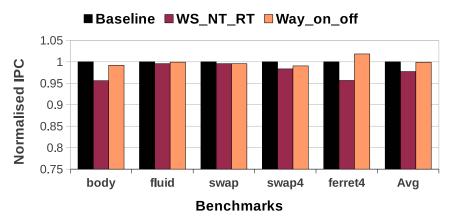

|   |     | Controlling IPC Degradation                         | . 123 |

|   |     | Overhead                                            | . 124 |

|   | 5.5 | Conclusion                                          | . 125 |

| 6 | DiC | CeR at LLC: Towards Controlling Temperature in TCMP | 127   |

|   | 6.1 | Introduction                                        | . 128 |

|   | 6.2 | Thermal issues: from LLC perspective                | . 130 |

|   |     | 6.2.1 LLC: Thermal Characteristics                  | . 130 |

|   |     | 6.2.2 Thermal Management: Core vs Cache             | . 131 |

|   |     | 6.2.3 Modeling Tile Temperature in TCMP             | . 132 |

|   | 6.3 | Performance Linked Thermal Management with DiCeR    | . 133 |

|   |     | 6.3.1 Target Bank Selection                         | . 135 |

|   |     | 6.3.2 Reconfiguring the LLC                         |       |

|   |     | 6.3.3 Algorithmic Design                            | . 137 |

|   | 6.4 | Experimental Analysis                               | . 139 |

|   |     | 6.4.1 Simulation Setup                              |       |

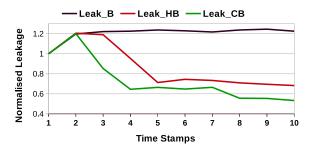

|   |     | 6.4.2 Temporal effect of cache resizing             | . 140 |

|   |     | 6.4.3 EDP gain                                      |       |

|   |     | 6.4.4 Effect on Tile and Chip Thermal Profile       |       |

|   |     | 6.4.4.1 Temporal Variation                          |       |

|   |     | 6.4.4.2 Thermal Stability                           |       |

|   |     | 6.4.4.3 Spatial Variation                           |       |

|   |     | $6.4.4.4$ Scalability $\ldots$                      |       |

|   |     | 6.4.5 Varying Reconfiguration Interval              |       |

|   |     | 6.4.6 Summary                                       |       |

|   | 6.5 | Conclusion                                          |       |

| _ |     |                                                     |       |

| 7 |     | CeR in a CCMP Towards Improving Thermal Efficiency  | 157   |

|   | 7.1 | Introduction                                        |       |

|   | 7.2 | Background                                          |       |

|   |     | 7.2.1 CCMP and its Leakage Hungry LLC               |       |

|   |     | 7.2.2 Thermal Potential of the Centralised LLCs     |       |

|   |     | 7.2.3 Runtime Cache Behaviour                       |       |

|   | 7.3 | Preliminaries and Analytical Problem Formulation    |       |

|   |     | 7.3.1 Core Temperature Modeling                     |       |

|   |     | 7.3.2 Problem Formulation                           |       |

|   |     | 7.3.3 Performance Modeling with Cache Size          |       |

|   |     | 7.3.4 Thermal Model                                 |       |

|   |     | 7.3.5 Combined Analytics                            | . 171 |

|   |     | 7.3.6 Finding out Optimal $b$                       | . 171 |

|   |     |                                                     |       |

|   |     | 7.3.7   | Patterns for Cache Resizing     |

|---|-----|---------|---------------------------------|

|   | 7.4 | DiCeF   | R for Thermal Efficiency        |

|   |     | 7.4.1   | Algorithms and Discussions      |

|   | 7.5 | Exper   | imental Evaluation              |

|   |     | 7.5.1   | Simulation Setup                |

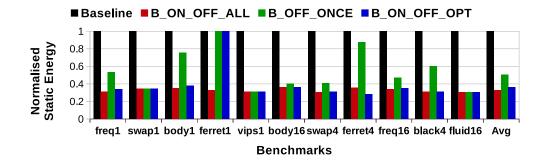

|   |     | 7.5.2   | Leakage Energy and EDP Savings  |

|   |     | 7.5.3   | DiCeR Overhead in CCMP          |

|   |     | 7.5.4   | On-Chip Thermal Profile         |

|   |     | 7.5.5   | Comparison with Greedy DVFS [2] |

|   |     |         | 7.5.5.1 Spatial Thermal Status  |

|   |     |         | 7.5.5.2 Effect on Performance   |

|   |     |         | 7.5.5.3 Summary                 |

|   |     | 7.5.6   | Evaluating the Scalability      |

|   | 7.6 | Conclu  | usion                           |

| _ | ~   |         |                                 |

| 8 | Con | nclusio | n and Future Work 193           |

|   | 8.1 | Summ    | ary of Contributions            |

|   | 8.2 | Scope   | for Future Work                 |

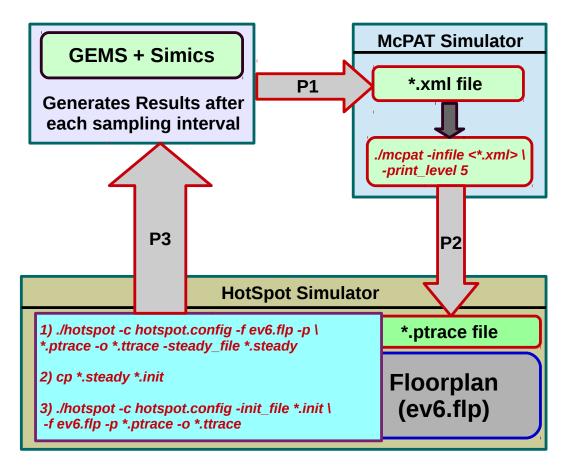

| A Closed Loop Simulation Framework        | 199 |

|-------------------------------------------|-----|

| TCMP and CCMP Architecture                | 199 |

| A.1 Components at Core area and L2 Cache  | 200 |

| A.2 Initial Simulator setup and Floorplan | 201 |

| HotSpot Configuration [hotspot.config]    | 204 |

| Floorplan Descriptions [ev6.desc]         | 205 |

| Average Power Consumption [avg.p]         | 205 |

| Floorplan as Output [output.flp]          | 207 |

| A.3 A few fixed McPAT Parameters          | 209 |

| A.4 Closed Loop Simulation                | 211 |

| A.4.1 Data Flow in Closed Loop Simulation | 212 |

| P1                                        | 212 |

| P2                                        | 213 |

| P3                                        | 213 |

|                                           |     |

| Bibliography                   | 215 |

|--------------------------------|-----|

| Publications Related to thesis | 233 |

# List of Figures

| 1.1  | Modern CMPs: Design and Floorplan outlines                              | 4   |

|------|-------------------------------------------------------------------------|-----|

| 1.2  | A Tiled CMP and a CMP with Centralised LLC.                             | 7   |

| 1.3  | Power consumed by Niagara2 Chip at different temperatures               | 12  |

| 1.4  | Change in Average Chip temperature during process execution             | 13  |

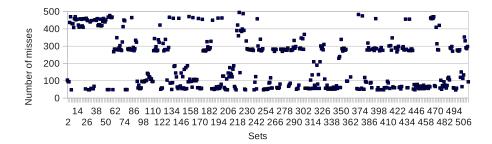

| 2.1  | Variable bank usages across different benchmarks in a TCMP as           |     |

| 2.2  | shown in Figure 1.2(a)                                                  | 26  |

|      | Figure 1.2(b)                                                           | 26  |

| 2.3  | Set usage profile of a bank in a TCMP. In case of CCMP too, this        | 00  |

| 0.4  | non-uniform pattern exists                                              | 28  |

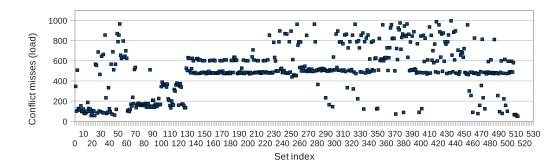

| 2.4  | An example of CMP-SVR                                                   | 29  |

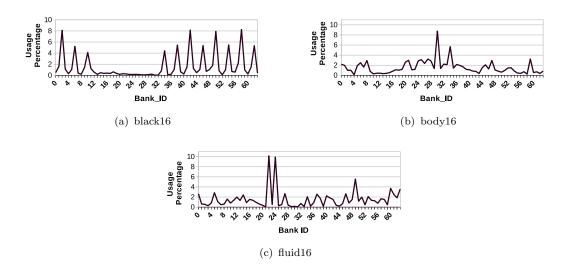

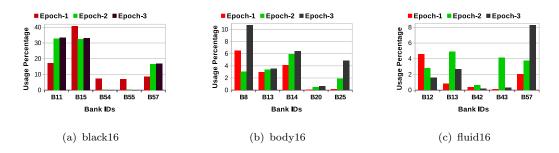

| 2.5  | Temporal Change in Bank Usages for different applications in a          | 0.1 |

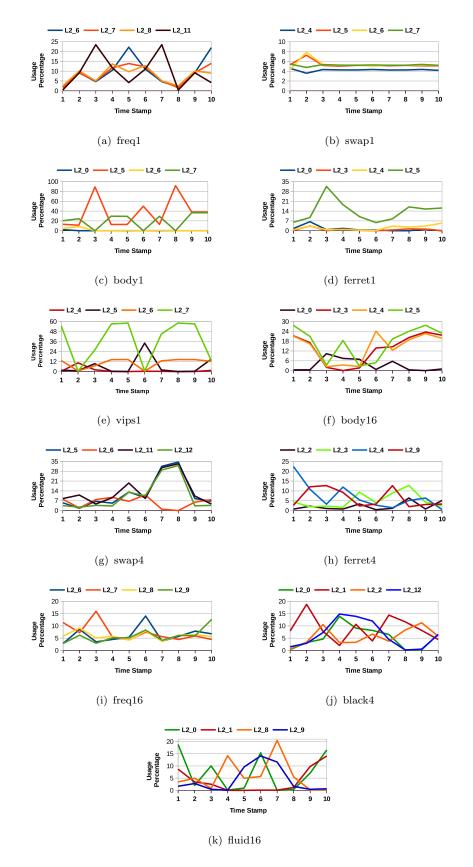

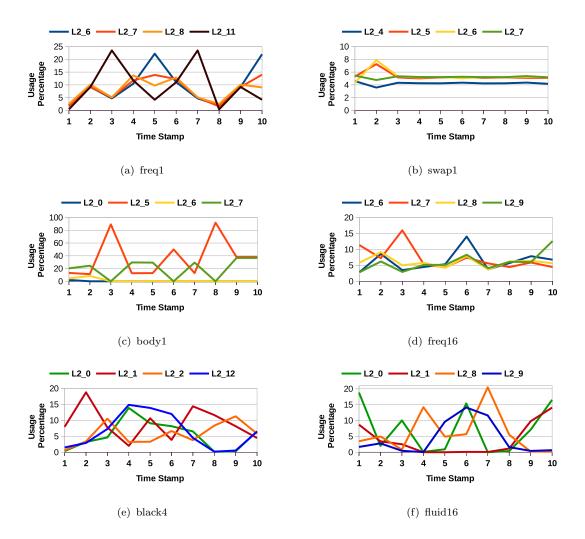

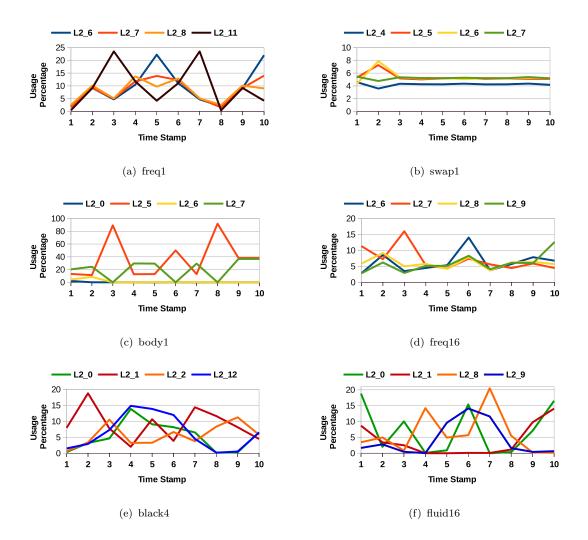

| 0.0  | TCMP having 16 banks.                                                   | 31  |

| 2.6  | Change in cache bank access behaviour over time in a CCMP having        | 20  |

| ~ -  | 64 banks.                                                               | 32  |

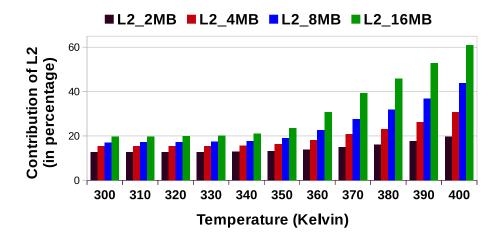

| 2.7  | Contribution of LLCs to the total Chip power consumption                | 35  |

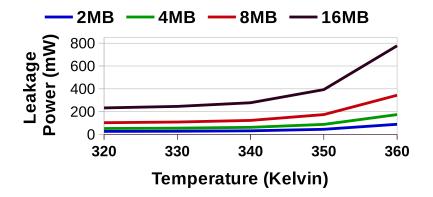

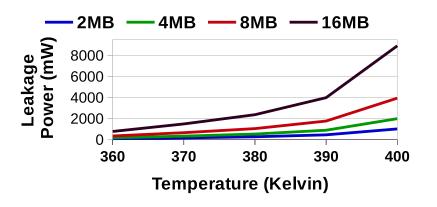

| 2.8  | Increment in Cache Leakage Power in low temperature                     | 36  |

| 2.9  | Increment in Cache Leakage Power in high temperature                    | 36  |

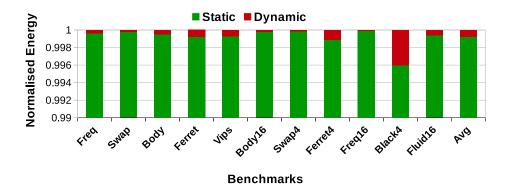

| 2.10 | Distribution of Power Consumption in an 8MB L2 cache                    | 36  |

| 2.11 | Classification of cache tuning techniques from a power/performance      |     |

|      | perspective.                                                            | 37  |

| 2.12 | Cache leakage reduction method at circuit level                         | 42  |

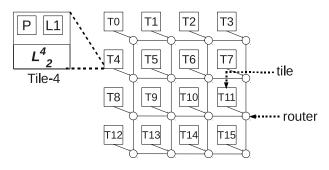

| 4.1  | Tiled CMP architecture                                                  | 80  |

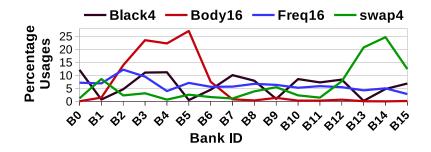

| 4.2  | Variable bank usages across different benchmarks                        | 81  |

| 4.3  | Temporal Change in Bank Usages for 6 different PARSEC applica-          |     |

|      | tions                                                                   | 82  |

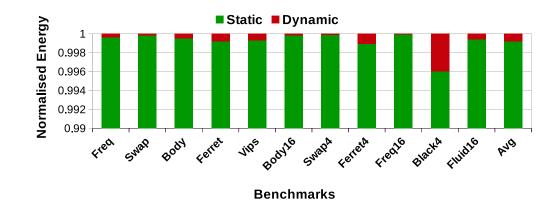

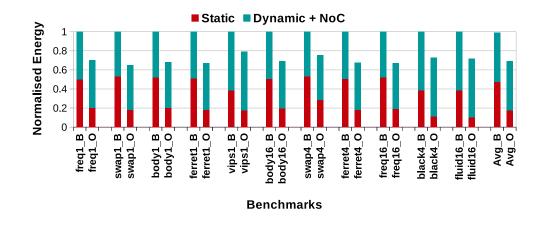

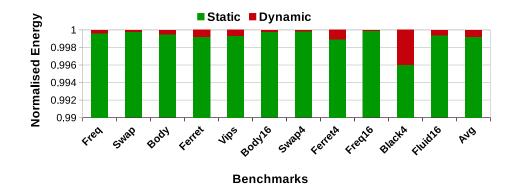

| 4.4  | Distribution of static and dynamic energy consumption of on-chip        |     |

|      | Last Level Caches(LLCs). Benchmarks are put in X-axis. Suffix '-B'      |     |

|      | implies that, simulation results are obtained in baseline architecture. | 83  |

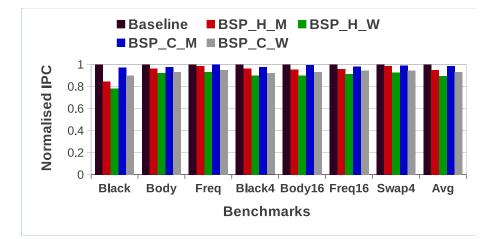

| 4.5  | Comparison between Migration (BSP_H_M, BSP_C_M) and Write-              |     |

|      | Back (BSP_H_W, BSP_C_W) policies in terms of IPC, while turning         |     |

|      | off some heavily used and lightly used L2 banks                         | 86  |

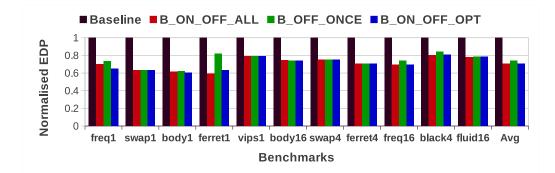

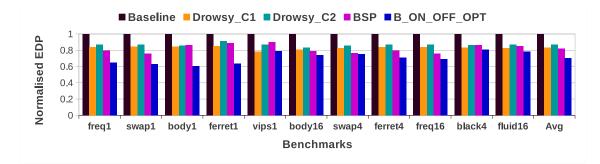

| 4.6  | Energy Delay Product obtained in proposed policies over the base-       |     |

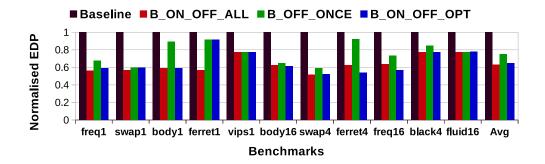

|      | line, BSP and Drowsy, with 4MB L2 cache. A smaller value is better.     | 93  |

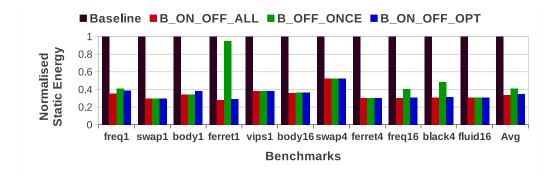

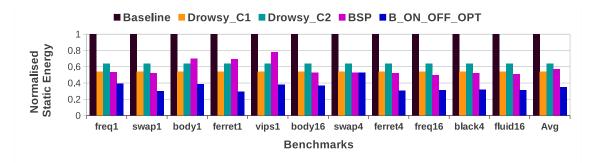

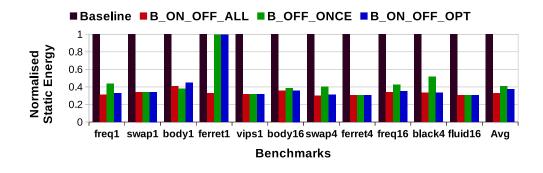

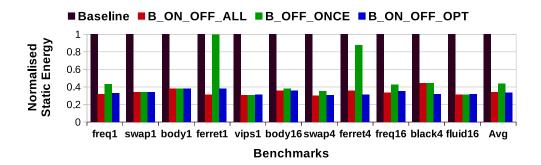

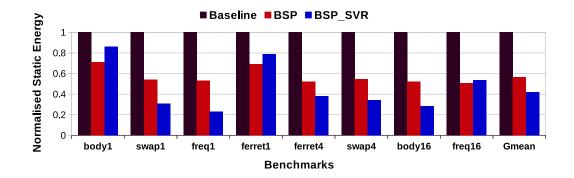

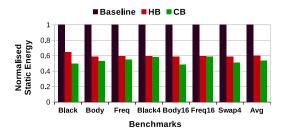

| 4.7  | Normalised static energy consumption, with 4MB L2 cache                 | 94  |

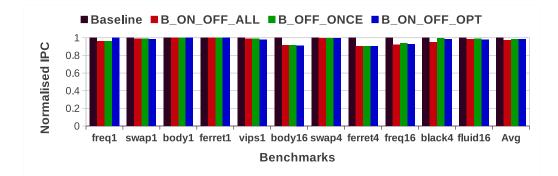

| 4.8  | Normalised IPC value for different benchmark applications, with 4MB L2 cache.                                                             | 95       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----------|

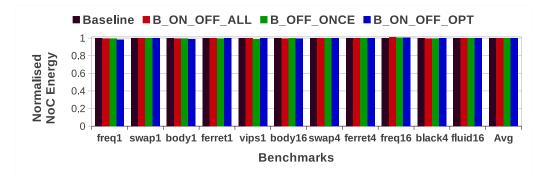

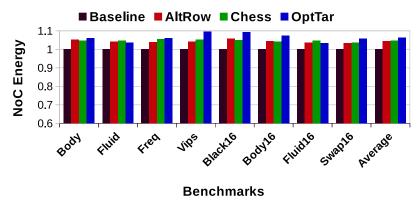

| 4.9  | Normalised network energy value for different benchmark applica-<br>tions, with 4MB L2 cache                                              | 95       |

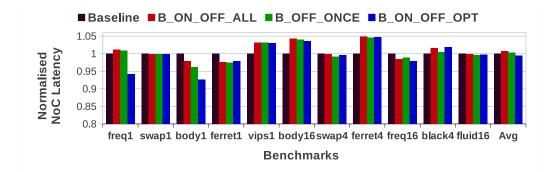

| 4.10 | Normalised NoC latency for different benchmark applications, with 4MB L2 cache.                                                           | 96       |

| 4.11 | Normalised total energy consumption with details breakdown of its components, for different benchmark applications, with 4MB L2           | 07       |

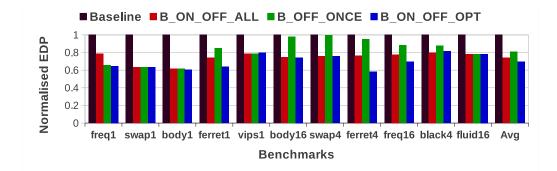

| 4.12 | cache                                                                                                                                     | 97<br>98 |

| 4.13 | Normalised static energy consumption for B_ON_OFF_OPT and compared with BSP and Drowsy, with 4MB L2 cache                                 | 98<br>98 |

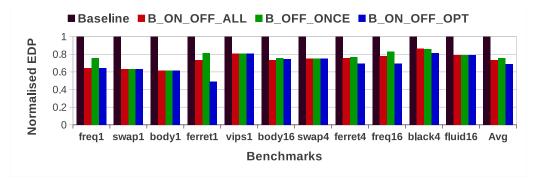

| 4.14 | Normalised EDP value for different benchmark applications for IPC degradation threshold = 2, with 4MB L2 cache                            | 99       |

| 4.15 | Normalised EDP value for different benchmark applications for IPC degradation threshold = 4, with 4MB L2 cache.                           | 99       |

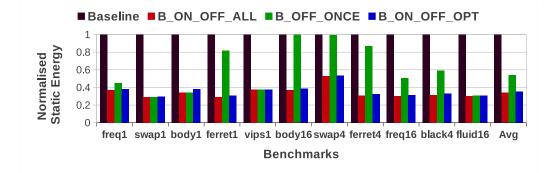

| 4.16 | Normalised static energy value for different benchmark applications for IPC degradation threshold = 2, with 4MB L2 cache                  | 100      |

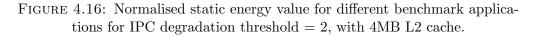

| 4.17 | Normalised static energy value for different benchmark applications<br>IPC degradation threshold = 4, with 4MB L2 cache                   |          |

| 4.18 | Normalised EDP value for different benchmark applications for IPC degradation threshold = 2, with 8MB L2 cache. $\dots \dots \dots \dots$ | 102      |

| 4.19 | Normalised EDP value for different benchmark applications for IPC degradation threshold = 3, with 8MB L2 cache. $\dots \dots \dots \dots$ | 102      |

| 4.20 | Normalised EDP value for different benchmark applications for IPC degradation threshold = 4, with 8MB L2 cache. $\ldots$ .                | 102      |

| 4.21 | Normalised static energy value for different benchmark applications for IPC degradation threshold = 2, with 8MB L2 cache                  | 103      |

|      | Normalised static energy value for different benchmark applications<br>for IPC degradation threshold = 3, with 8MB L2 cache               | 103      |

| 4.23 | Normalised static energy value for different benchmark applications IPC degradation threshold = 4, with 8MB L2 cache. $\ldots$ .          | 103      |

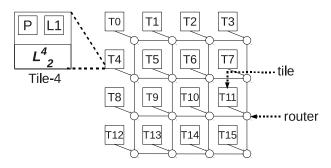

| 5.1  | Tiled CMP architecture                                                                                                                    |          |

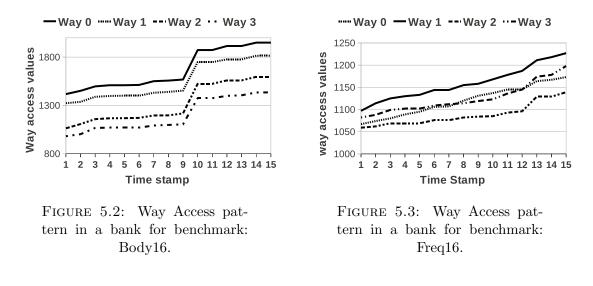

| 5.2  | Way Access pattern in a bank for benchmark: Body16                                                                                        |          |

| 5.3  | Way Access pattern in a bank for benchmark: Freq16                                                                                        |          |

| 5.4  | Set usage profile of a bank in a TCMP                                                                                                     |          |

| 5.5  | Savings in Static Energy with BSP_SVR                                                                                                     |          |

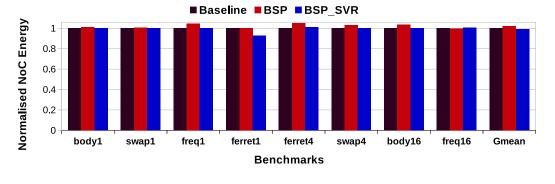

| 5.6  | Savings in NoC Energy with BSP_SVR                                                                                                        |          |

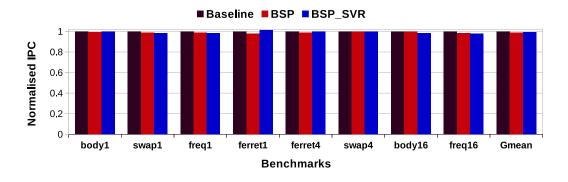

| 5.7  | Change in IPC: BSP vs BSP_SVR                                                                                                             |          |

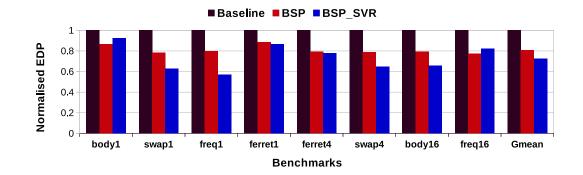

| 5.8  | EDP gains: BSP vs BSP_SVR.                                                                                                                |          |

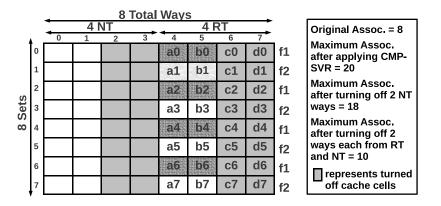

| 5.9  | Way shutdown using CMP-SVR.                                                                                                               | 118      |

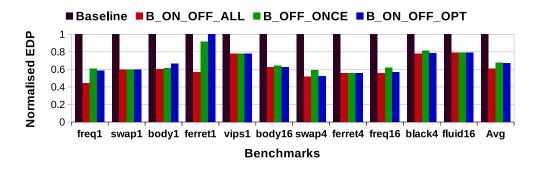

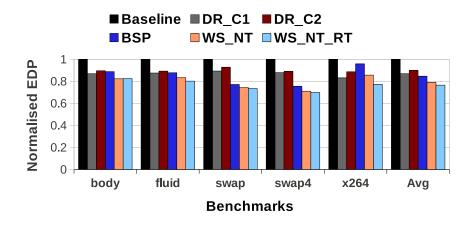

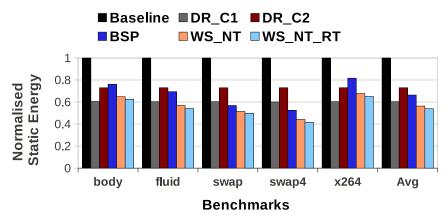

| 5.10 | Savings in EDP in comparison with BSP and Drowsy Cache for 4MB 4-way L2.                                                                  | 121      |

| 5.11 | Savings in Static Energy in comparison with BSP and Drowsy<br>Cache for 4MB 4-way L2                   |

|------|--------------------------------------------------------------------------------------------------------|

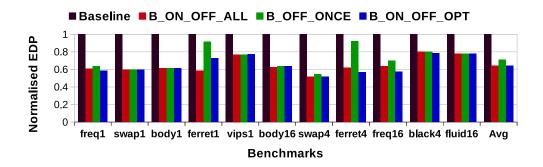

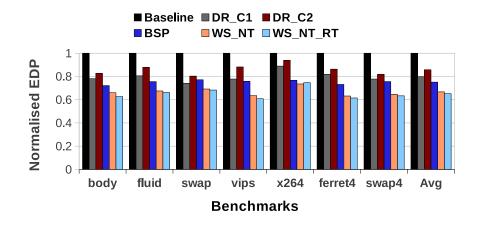

| 5.12 | Savings in EDP in comparison with BSP and Drowsy Cache for                                             |

|      | 4MB 8-way L2                                                                                           |

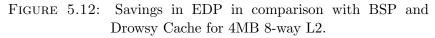

| 5.13 | Savings in Static Energy in comparison with BSP and Drowsy<br>Cache for 4MB 8-way L2                   |

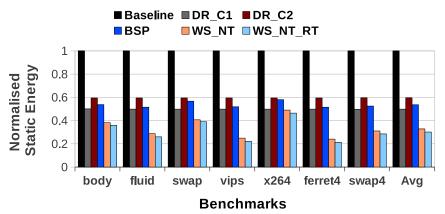

| 5.14 | Normalised EDP gains for 2MB 8-way L2 with respect to baseline 123                                     |

| 5.15 | Normalised Static Energy values for 2MB 8-way L2 with respect to baseline                              |

| 5.16 | Normalised Static Energy values for 2MB 8-way L2 for way-off as well as way turn-on policy             |

| 5.17 | Normalised IPC values for 2MB 8-way L2 for way-off as well as way                                      |

|      | turn-on policy. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $124$ |

| 6.1  | Tiled CMP architecture                                                                                 |

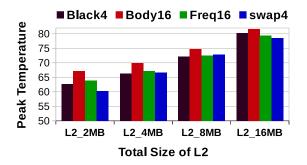

| 6.2  | Peak Temperature of Caches in °C                                                                       |

| 6.3  | Temporal Change in Bank Usages for 6 different PARSEC applica-                                         |

|      | tions                                                                                                  |

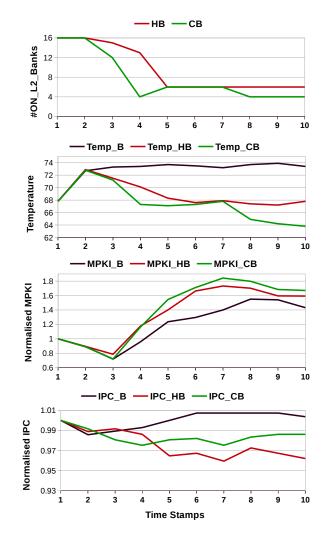

| 6.4  | Temporal effect of cache resizing: body16                                                              |

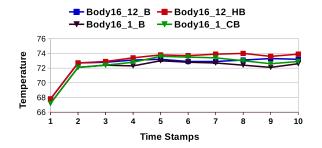

| 6.5  | Thermal status of target banks in HB and CB, for Body16 142                                            |

| 6.6  | Change in cache leakage in HB and CB, for Body16                                                       |

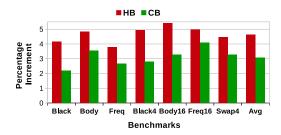

| 6.7  | Increment in NoC latency than Baseline                                                                 |

| 6.8  | Increment in NoC Energy than Baseline                                                                  |

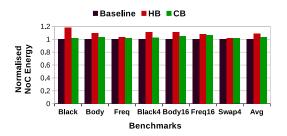

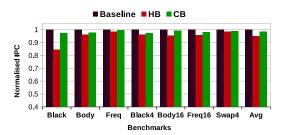

| 6.9  | Change in IPC with respect to baseline                                                                 |

| 6.10 | Reduction in leakage energy for HB and CB than baseline 143                                            |

| 6.11 | EDP gain for HB and CB over baseline                                                                   |

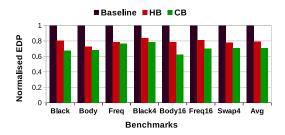

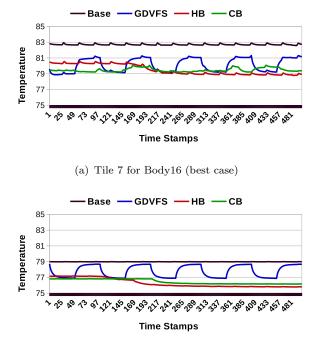

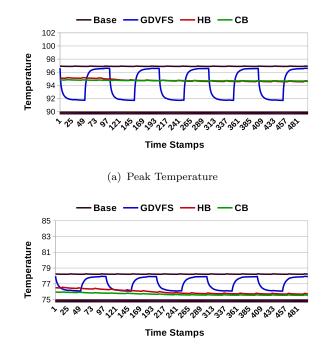

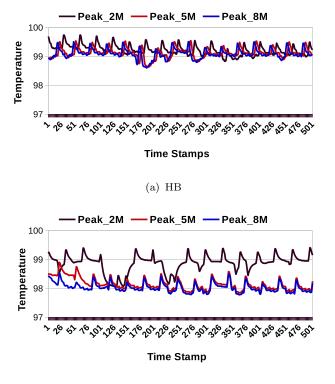

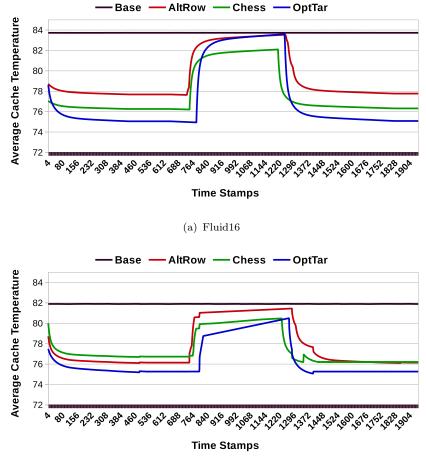

| 6.12 | Temporal Thermal variation of a tile                                                                   |

| 6.13 | Temporal change in Chip Temperature of Body16. (best case) 145                                         |

| 6.14 | Temporal Change in Chip Temperature of Freq. (worst case) 146                                          |

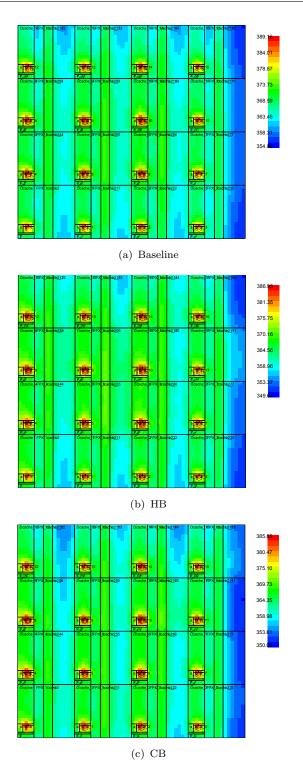

| 6.15 | Spatial Thermal variation of the Chip for Body16                                                       |

| 6.16 | Change in Average Tile Temperature for Body16                                                          |

| 6.17 | Reduction in Peak Temperature for different cache sizes 150                                            |

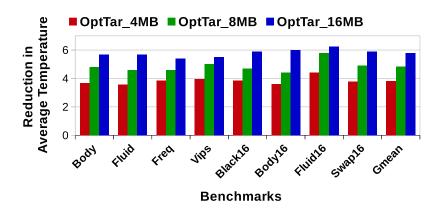

| 6.18 | Reduction in Average Chip Temperature for different cache sizes 151                                    |

| 6.19 | Temporal Change in Peak Temperature of Body16 while varying                                            |

|      | Reconfiguration Interval                                                                               |

| 6.20 | Temporal Change in Average Temperature of Body16 while varying                                         |

|      | Reconfiguration Interval                                                                               |

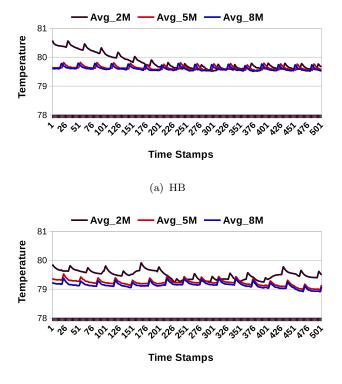

| 7.1  | CMP architecture with Centralised LLC (CCMP)                                                           |

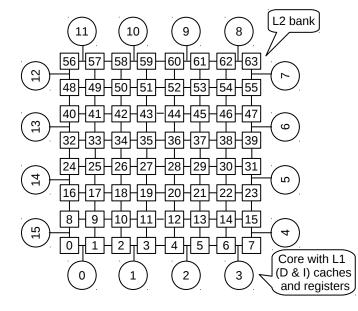

| 7.2  | Percentage contribution for all the on-chip components collected                                       |

|      | by simulating our baseline CCMP architecture (ref. Figure 7.1)                                         |

|      | in McPAT having 16 cores (from UltraSPARCIII family) and 64-                                           |

|      | banked 8MB L2 cache as centralised LLC                                                                 |

| 7.3  | Distribution of Power Consumption in an 8MB L2 cache 161                                               |

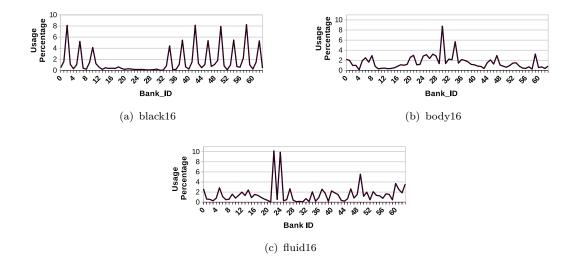

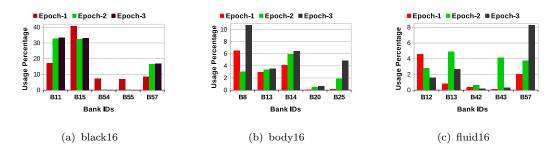

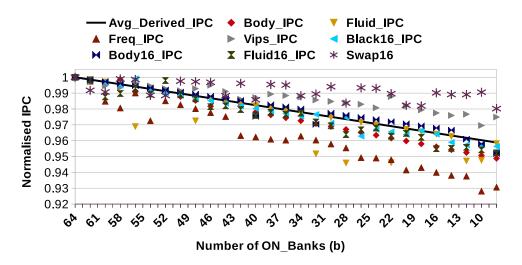

| 7.4  | Non uniform distribution of cache bank accesses in a CCMP like                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------|

|      | Figure 7.1                                                                                                                       |

| 7.5  | Change in cache bank access behaviour over time in a CCMP having                                                                 |

|      | 64 banks                                                                                                                         |

| 7.6  | Internals of our baseline CMP architecture                                                                                       |

| 7.7  | Relationship between IPC and Cache Size                                                                                          |

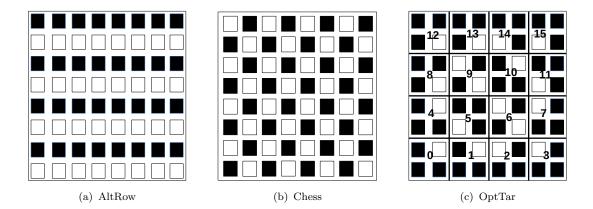

| 7.8  | L2 bank Shutdown patterns                                                                                                        |

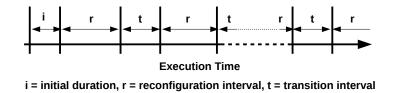

| 7.9  | The division of Execution time while implementing Algorithm 7 175 $$                                                             |

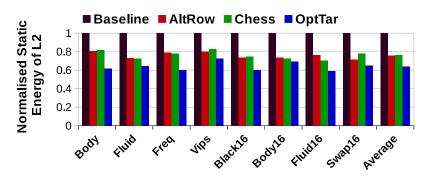

| 7.10 | Static Energy savings at L2 Cache                                                                                                |

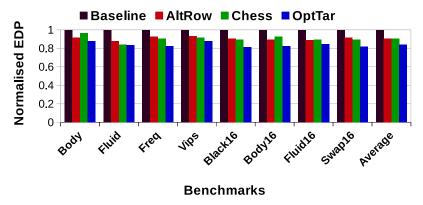

| 7.11 | EDP Savings of the chip                                                                                                          |

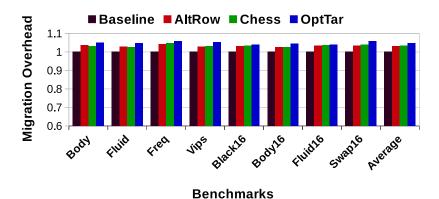

| 7.12 | $\label{eq:Migration} Migration \ Overhead. \ \ldots \ $ |

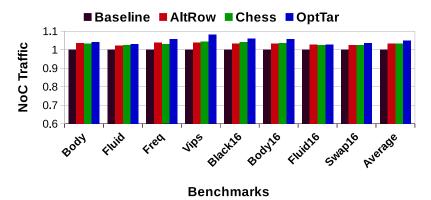

| 7.13 | Increment in NoC Traffic                                                                                                         |

| 7.14 | Increment in NoC Energy                                                                                                          |

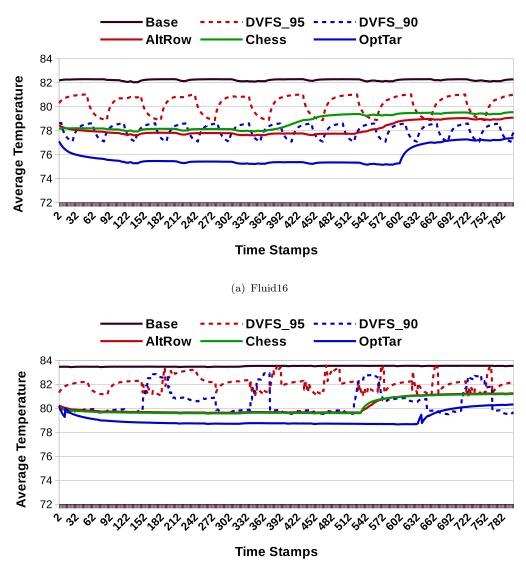

| 7.15 | Snapshot of temporal changes in <b>average</b> temperature of L2 during                                                          |

|      | execution                                                                                                                        |

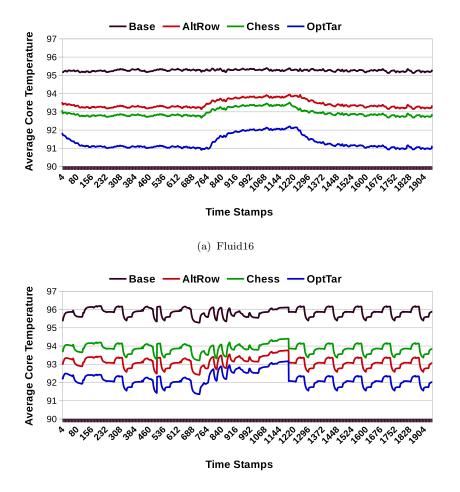

| 7.16 | Snapshot of temporal changes in <b>average</b> temperature of the cores                                                          |

|      | during execution                                                                                                                 |

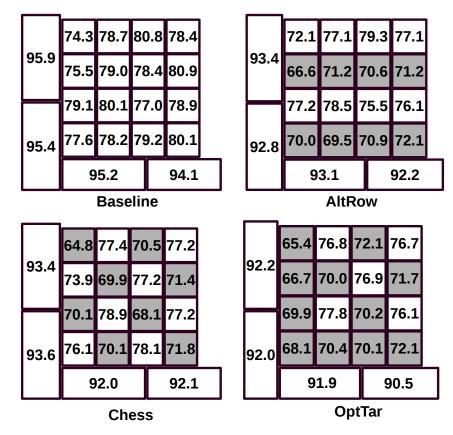

|      | Temperatures (in °C) of the individual banks during $\boldsymbol{r}$ , for Fluid16. 183                                          |

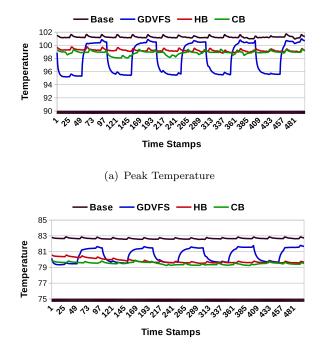

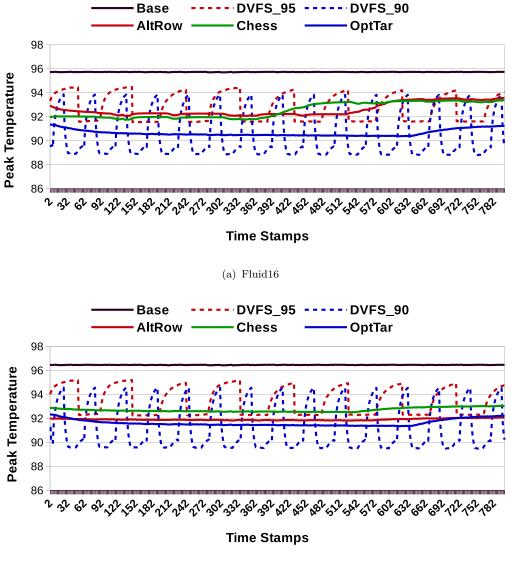

| 7.18 | Snapshot of temporal changes in <b>peak</b> temperature of the chip dur-                                                         |

|      | ing a sample reconfiguration interval $\boldsymbol{r}$                                                                           |

| 7.19 | Snapshot of temporal changes in <b>average</b> chip temperature during                                                           |

|      | a sample reconfiguration interval $r$                                                                                            |

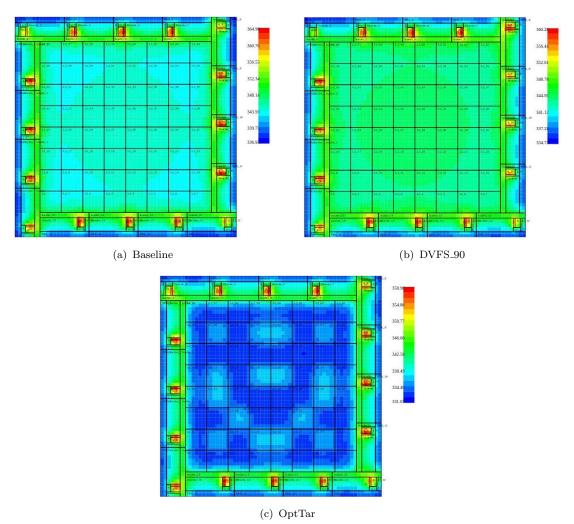

| 7.20 | On-chip spatial thermal behaviour generated by Hotspot 6.0 [3] for                                                               |

|      | Fluid16 at some certain instance during $r$ . Temperature Ranges                                                                 |

|      | for three configurations-(a) Baseline: $336K$ to $364K$ , (b) DVFS_90:                                                           |

|      | 334K to $360K$ , (c) OptTar: $332K$ to $358K$ . Red colour represents peak value where Blue represents the lowest temperature    |

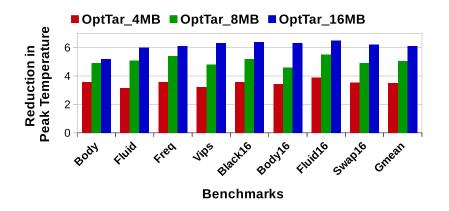

| 7 91 | Comparing temperature reduction (in °C) with different cache sizes. 191                                                          |

| 1.41 | Comparing temperature reduction (in C) with different cache sizes. 191                                                           |

| 8.1  | Summary of the thesis contributions                                                                                              |

| A.1  | A Tiled CMP and a CMP with Centralised LLC                                                                                       |

| A.2  | TCMP Floorplan   208                                                                                                             |

| A.3  | CCMP Floorplan                                                                                                                   |

| A.4  | Our Closed Loop Simulation Framework for thermal analysis 212                                                                    |

|      |                                                                                                                                  |

|      |                                                                                                                                  |

# List of Tables

| 1.1                                       | Power consumed by on-chip caches $[4, 5]$                                                                                                                                                                                                                     | 1 |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 3.1<br>3.2<br>3.3                         | The inherent key characteristics of Parsec benchmarks [6] 66<br>The data usage behavior of Parsec benchmarks [6]                                                                                                                                              | 8 |

| 4.1                                       | Maximum percentage of runtime IPC degradation with 4MB 4Way<br>L2 cache                                                                                                                                                                                       | 9 |

| 4.2                                       | Energy/Power values obtained from CACTI [7] for two different L2 cache configurations. In each of these cases, L2 is uniformly divided into 16 banks.                                                                                                         | 0 |

| 4.3                                       | System and Network Parameters                                                                                                                                                                                                                                 | C |

| 4.4                                       | CACTI Configurations                                                                                                                                                                                                                                          | 0 |

| <ul><li>4.5</li><li>4.6</li></ul>         | Summary of the results obtained from our experiments with respect<br>to baseline architecture. Here, <b>B_ON_OFF_ALL</b> , <b>B_OFF_ONCE</b><br>and <b>B_ON_OFF_OPT</b> are denoted by <b>B1</b> , <b>B2</b> and <b>B3</b> , respec-<br>tively, in this Table | 4 |

| 4.0                                       | to baseline for Drowsy cache [1] and <b>B_ON_OFF_OPT</b> (denoted<br>as <b>B3</b> in this Table ). <b>C1</b> and <b>C2</b> represents <b>Drowsy_C1</b> and<br><b>Drowsy_C2</b> , respectively                                                                 | 4 |

| $5.1 \\ 5.2$                              | CACTI Configurations                                                                                                                                                                                                                                          |   |

| 5.3                                       | Summary of improvement over baseline for a 4MB 8-way set asso-<br>ciative L2 cache                                                                                                                                                                            |   |

| C 1                                       |                                                                                                                                                                                                                                                               | 0 |

| 6.1                                       | System and Network Parameters    139      MaDAT and HatCriet Conference    120                                                                                                                                                                                |   |

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$ | McPAT and HotSpot Configurations                                                                                                                                                                                                                              | J |

| 0.5                                       | ature.                                                                                                                                                                                                                                                        | б |

| 6.4                                       | Standard deviation for temporal changes in Peak Temperature of                                                                                                                                                                                                | J |

| 0.1                                       | the Chip.                                                                                                                                                                                                                                                     | 7 |

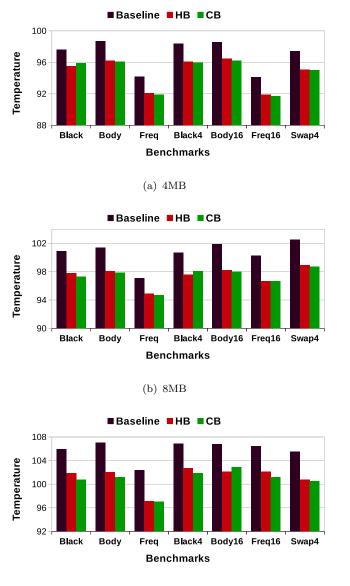

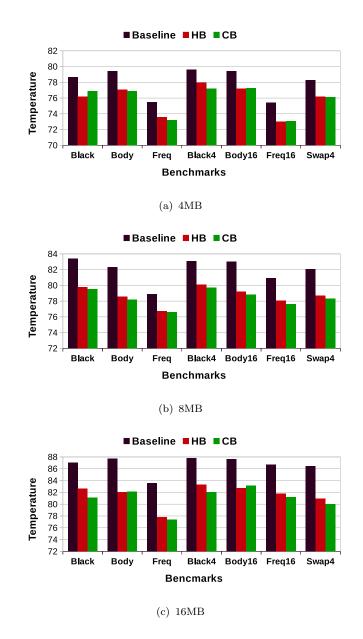

| 6.5                                       | 4MB L2 Cache                                                                                                                                                                                                                                                  |   |

| 6.6                                       | 8MB L2 Cache                                                                                                                                                                                                                                                  |   |

| 6.7                                       | 16MB L2 Cache                                                                                                                                                                                                                                                 | 4 |

| 7.1  | Size vs LLC's Peak Temperature (in °C)                             |

|------|--------------------------------------------------------------------|

| 7.2  | Descriptions of the notations used in our analytical modeling 165  |

| 7.3  | Description of Parameters used in Algorithm 7                      |

| 7.4  | System and Network Parameters                                      |

| 7.5  | McPAT and HotSpot Configurations                                   |

| 7.6  | V/F Settings for UltraSPARCIII (used in our simulation) 185        |

| 7.7  | Maximum Reduction in Peak Temperature (°C) of the Chip with        |

|      | respect to baseline                                                |

| 7.8  | Maximum Reduction in Average Temperature (°C) of the Chip with     |

|      | respect to baseline                                                |

| 7.9  | Standard Deviation: <b>Peak</b> Temperature of the Chip            |

| 7.10 | Standard Deviation: Average Temperature of the Chip 188            |

| 7.11 | Change in IPS with respect to baseline                             |

| 7.12 | Summary                                                            |

| A.1  | System and Network Parameters                                      |

| A.2  | Cache and Core Parameters for McPAT and HotSpot Configurations 210 |

|      |                                                                    |

# Abbreviations

| CMP     | Chip Multi-Processor                                        |

|---------|-------------------------------------------------------------|

| LLC     | Last Level Cache                                            |

| CPI     | Cycles Per Instruction                                      |

| LRU     | Least Recently Used                                         |

| MRU     | Most Recently Used                                          |

| AMAT    | Average Memory Access Time                                  |

| MPKI    | Miss Per Kilo (Thousand) Instructions                       |

| IPC     | Instructions Per Cycle                                      |

| NUCA    | Non Uniform Cache Access                                    |

| NoC     | Network on Chip                                             |

| SNUCA   | Static NUCA                                                 |

| DNUCA   | Dynamic NUCA                                                |

| TCMP    | Tiled based CMP                                             |

| CCMP    | CMP with Centralised on-chip LLC                            |

| DAM     | Dynamic Associativity Management                            |

| CMP-VR  | A DAM based architecture (Victim Retention)                 |

| CMP-SVR | A DAM based architecture (Set Associative Victim Retention) |

| RT      | Reserve sTorage                                             |

| NT      | Normal sTorage                                              |

| EDP     | Energy Delay Product (Energy $\times$ CPI)                  |

| TDP     | Thermal Design Power                                        |

| DVFS    | Dynamic Voltage & Frequency Scaling                         |

| DTM     | Dynamic Thermal Management                                  |

| IPS     | Instructions Per Second                                     |

## Chapter 1

## Introduction

A few years back, in the city of *Dieland* a job advertisement was published.

### Vacancy!! Vacancy!! Vacancy!!

A set of identically efficient employees are needed for information management at **Dieland Corporate House (DCH)**. The selected applicants have to maintain a set of information during office hours. They have to provide information to the foremen whenever needed, and have to manage the information carefully if foremen have modified it. The missing information, if any, has to be brought from the subordinates. Workload may vary with the situations.

**Reward-**UFS, the Uninterrupted Food Supply during office hours.

Almost a couple of weeks later, on a fine morning a set of identically efficient and jobless people came for the interview at the DCH-office. Surprised after seeing such a crowd, the manager arranged an interview and selected a chunk of people, who were found fit for the job. These newly appointed employees formed a group, named *Basket*. The governing body of DCH was very pleased with the situation and *Basket* started enjoying UFS facility during the office hours.

The first quarter was over. Everything was fine at the *Basket* end. However, suddenly one morning, the manager noticed something. Most members of *Basket* were busy with the appetiser whereas very few of them working hard with a mammoth amount of workloads; and another few having a bit lesser amount of work to handle. Hence, there was a mass of employees relaxing and energised heavily just by enjoying the UFS and creating disturbances at office. The manager was worried about the horrified situation and tried hard to get a solution. Alas! no idea clicked in his wobbly mind even after thinking continuously round the clock for over a week.

At the beginning of the next week, while buying fuel for his car, an idea came to manager's mind. "UFS!! the principal fuel of *Basket...*should be restricted right now!!...no food supply to the idle ones." On his way to office, the rules were prepared and thrown in the *Basket. Basket* opened the rule-book and the rules revealed:

- (R1) More food consumption is bad for one's health and may reduce your lifetime. Therefore, food will be supplied only when you will work and be honest in helping others.

- 2. (R2) Rearrange/Optimise the movements of your organs in such a way that you can provide the same performance with lesser amount of food as only some of your body-parts will be active.

- 3. (R3) Those who handle heavy workloads are allowed to sleep for a stipulated time-span (hence no food supply); UFS is however restricted to the people having lesser or no workloads to handle.

- 4. (R4) Recently, we have noticed that, some of you have become over energised due to UFS and are disturbing the foremen adjacent to you. Hence, there will be restricted food supply to the neighbours of the foremen.

To get rid of these rules, a meeting was arranged where the whole *Basket* decided to resign from DCH. Meanwhile, the whole corporate world of *Dieland* started following the same set of rules, which *Basket* was not accepting. Finally, the news spreaded all over and soon, the *Basket* returned back at DCH following the set of rules.

When I came to know about this tale of *DCH*, from a computer architect's point of view, I was surprised that, the characters can be mapped and fixed well in my domain. Making the foremen as CPU cores and Basket as caches with manager as the cache controller, the scenario can be visualised well enough in the world of real computer hardware.

Basically, over the past decade (with end of Dennard Scaling [8]), the singlecore systems touched the upper-limit of maximum attainable performance, i.e. the highest operating frequency, primarily due to its higher power consumption. The architects and designers got motivations from this to develop processor chips with multiple cores that can operate at lower voltages and frequencies than their single core counterparts, while offering the same performance with lesser power consumption. Furthermore, the ever increasing demand of processing power to run modern heavy applications needs heavy amount of parallel processing, which can no longer be satisfied with single core systems. With due consideration to Moore's Law for on-chip transistor counts, and depending upon the modern integration technology, the number of cores in a chip is expected to increase every year [9, 10]. This integration of multiple cores on a single chip is known as Chip Multi-Processors (CMPs).

### 1.1 Modern Chip Multi-Processors (CMPs)

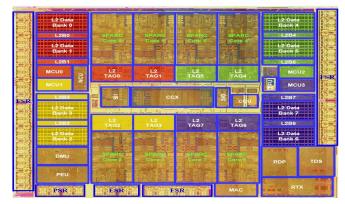

Modern CMPs are usually equipped with a large number of cores, each with same (homogeneous) or different (heterogeneous) processing power. To commensurate the high data demand of these cores, multi-level on-chip caches (i.e. the *Basket* of DCH) are attached [11]. Eventually, the large CMPs need strong communications among all of its components, which can be offered by a modern on-chip network system, called as Network on-Chip (NoC). Figure 1.1 shows floorplan outlines and designs for two modern CMPs- UltraSPARC T2 and Nehalem [12].

(a) UltraSPARC T2 [13]

(b) Nehalem [10]

FIGURE 1.1: Modern CMPs: Design and Floorplan outlines

### 1.1.1 Components in CMPs

On-chip components of a modern CMP can be classified into three categories:

- 1. CPU Cores. as the computational units.

- 2. On-chip Caches. to accumulate most recently used data on the chip.

- 3. Network-on-Chip. for communicating among the on-chip components.

Computational performance refers to how much time the system takes to execute an application. It is usually measured in terms of Total Execution Time, Instructions Per Cycle (IPC), Instructions Per Second (IPS), speed-up factor to a base system, etc [14]. The resulting performance in a CMP further depends on how much parallelisation is achieved while the application is executed. The parallelisation is achieved by multi-threading where an application is grained into a certain number of threads.

Depending upon the nature of majority of its instructions, an application is tagged either as Compute Bound or Memory Bound [15, 16, 17, 6]. In the case of memory bound application, most of its instructions need to access memory. Hence, system performance has direct dependency upon both core's clock frequency and memory latency. Memory latency further depends upon the following: (I) How quickly memory finds the desired block after it has been requested, (II) How fast the data reaches to the core from the memory subsystem. Former one depends upon the type and structure of the memory, whereas latter one relies on NoC performance. The equation for Execution Time can be formulated as:

$$Total\_Exec\_Time = Computation\_Time + Memory\_Cycles + NoC\_Latency$$

(1.1)

#### 1.1.1.1 On-Chip Caches

The rapid progress in VLSI technology, and reduced channel length of modern transistors [9] help architects and chip designers to integrate more on-chip cores with the larger multi-level on-chip caches. Caches are labeled according to their distance from the CPU cores. The nearest (i.e. higher) level caches to the cores are named as L1 caches, and next (i.e. comparatively lower) level is named as L2 and so on [14]. However, among all levels of on-chip caches Last Level Caches (LLCs) are the largest in size and occupy a significant area on the wafer real-estate (ref. Figure 1.1). Recent CMPs usually have two to three levels of on-chip caches,

out of which, mostly the LLC is kept as shared cache space, whereas rest are made private to the cores [12].

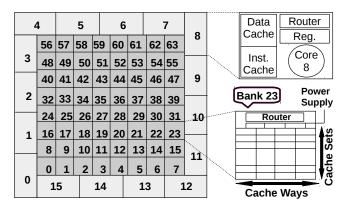

Accessing a large cache for every memory operation is both time consuming and incurs more power. Additionally, the large on-chip caches are accounted for their significant contributions in total on-chip power consumption. To mitigate this issue, architects split the whole large cache physically into a number of identical slices, each of them is called as cache bank. When the large cache is divided into banks, the division may follow either of the two patterns-(a) set wise distribution, where all ways of a set are present in a same bank, (b) way wise distribution, where a particular way of all the sets are kept in the same bank. Some optimised structures also follow a mixed distribution of the above two. The multi-banked caches not only reduce the access latency but also provide more space to the circuit designers for power optimisation.

Data in the caches are stored as cache blocks. For a CMP, these cache blocks/locations may maintain a uniform (UCA) or non-uniform (NUCA) cache access time from the cores. Most of the state-of-the-art CMPs follow NUCA architectures, as maintaining uniform latency with larger caches when coupled with a large set of cores is impractical. In the case of NUCA, cache blocks can be accessed with lesser latency if the blocks are located near to the requesting core, and reverse situation may also arise, which drastically curtails system performance. Static NUCA (SNUCA) always maintains a fixed cache location for a particular block, whereas Dynamic NUCA (DNUCA) moves the block to the close proximity of the requester core [18]. However, too much block movements across the larger cache increase power consumption in DNUCA. The proposed designs given in this thesis use the multi-banked SNUCA LLC structure with set wise distribution.

While fetching cache blocks from the lower level memory to multi-level caches, data allocation can follow either multi-level inclusion or multi-level exclusion property. In the former one, cache blocks present at the higher levels are the proper subset of the blocks present at the lower level caches. Whereas in the latter one, blocks

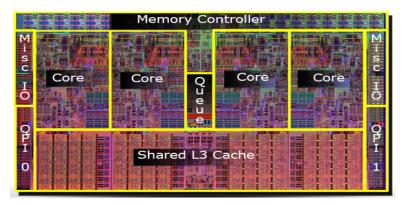

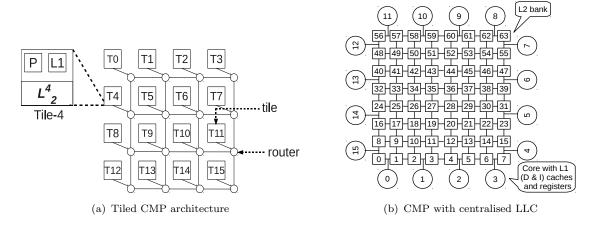

FIGURE 1.2: A Tiled CMP and a CMP with Centralised LLC.

present across the cache levels are disjoint. In this thesis, we use multi-level inclusive caches.

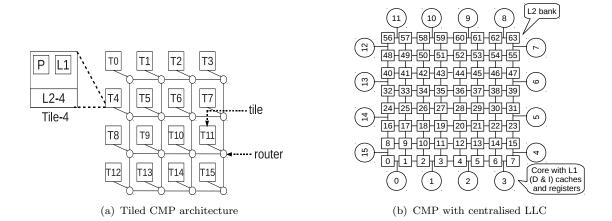

#### 1.1.1.2 Placement of LLCs

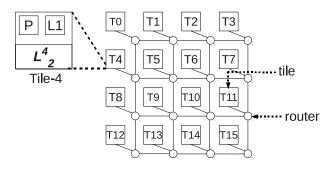

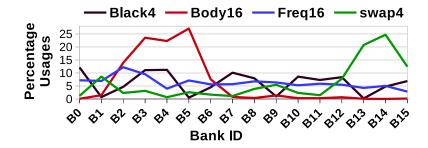

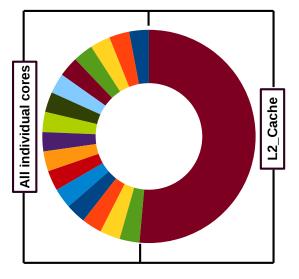

**Tiled CMP (TCMP)** A Tiled CMP architecture divides the chip into multiple number of identical tiles [19, 18]. Figure 1.2(a) depicts a model of a Tiled CMP, where the chip is constructed by 16 identical tiles. Each of them contains a CPU core with its private L1 Data & Instruction caches, and an L2 cache bank. A 2D mesh NoC [20] connects all the 16 tiles to form the whole chip. Each of the tiles is also associated with its own router for communicating through the NoC with other tiles. The L2 cache is here physically distributed but all banks are shared among the 16 cores. Accessing a data block from the home L2 bank (i.e. the bank located with the same tile of the requester core) incurs less latency than the far remote banks (located in some other tiles). L2 is considered here as on-chip LLC. The number written in each tile (like T4) represents the tile id. The tiles are numbered from 0 to 15.

**CMP with Centralised LLC (CCMP)** In case of CCMP, the whole chip is also divided into several tiles, where the tiles are not identical. Each tile either contains an LLC bank or can contain a core along with its private L1 Data &

Instruction caches. The LLCs are large in size and mostly the number of banks are more and placed centrally. Figure 1.2(b) illustrates the architecture, where 16 cores are available and tiles containing cores are located along the periphery of the CMP. Note that, in this figure, L2 is considered as the on-chip LLC similar to TCMP architecture.

### 1.2 Power Consumption in CMPs

For each of the on-chip components, the total power consumption can be divided into three major parts [4, 21, 22]-(A) Dynamic Power, (B) Static Power and (C) Short Circuit Power.

### 1.2.1 Dynamic Power

Dynamic Power is consumed due to switching activity of the transistors present on-chip due to charging/discharging of the output capacitances. However, for computational elements dynamic power is nothing but the processing power which can be written as follows [23, 22]-

$$P_{Dyn} = \alpha. C. V^2. f \tag{1.2}$$

$P_{Dyn}$  represents the dynamic power of the cores, and  $\alpha$ , C, V and f denote activity factor, capacitance, supply voltage and running frequency of the core, respectively, which indicates that, core's power consumption has direct dependency on its operating frequency.

For the on-chip caches, dynamic power is consumed during cache accesses. The cache is accessed either for a read operation or for a write operation. Usually, in the case of cache memory (constructed with SRAM cells), reading and writing power consumption are almost the same [7, 21, 24]. The detailed power/energy model of the cache is discussed in the next chapter.

The NoC of any CMP is constructed with two basic components-(a) Routers and (b) Connecting Links. The routers are complicated part of NoC which use several routing algorithms for sending data optimally across the chip. The data is transmitted through the Links, which are primarily a set of metal wires. Routers consume dynamic power during routing operations which usually comes from three basic sub-parts of routers [25]-

- Router Clock- The essential component of any synchronous design.

- FIFO Buffers- That maintain the order/sequence of incoming/outgoing data blocks.

- Allocators and Arbiters- That channelise data blocks to reach the proper destinations.

### 1.2.2 Static Power

On-chip circuitry draws some amount of power even when the circuit is not performing any job, so this power is termed as static power. The static power mainly indicates the circuit's leakage power which is due to two important leakage components-(a) Subthreshold Leakage and (b) Gate Leakage [23, 22, 26, 27]. The former one has direct dependency with the supply voltage and running chip temperature. High chip temperature breaks the co-valent bonds in the atoms of semiconductor materials and releases electrons which start flowing through the reverse bias, and draws a current, called Subthreshold Leakage current. The power consumed due to this Subthreshold Leakage current is known as Subthreshold Leakage power. On the other hand, down-scaling device size reduces the thickness of gate-oxide materials, which increases the Gate Leakage power. The detailed analysis of the root causes of leakage power is out of scope of this thesis. Following equation shows the direct dependency of subthreshold leakage upon the running temperature and supply voltage [28, 23]:

$$P_{s} = K_{1} V_{DD} T^{2} e^{(\alpha V_{DD} + \beta)/T)} + K_{2} e^{(\gamma V_{DD} + \delta)}$$

(1.3)

$P_s$  denotes the static power consumption due to subthreshold leakage for a CMOS circuit.  $V_{DD}$  is the supply voltage and T implies the current temperature.  $K_1$ ,  $K_2$ ,  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\delta$  are the empirical constants which represent different circuit parameters.

#### 1.2.3 Short-Circuit Power

This power is consumed due to non-zero rise/fall time of the CMOS circuitry. A very short time-span when both NMOS and PMOS are active simultaneously, makes a direct link between supply voltage and ground. This power consumption is very negligible and often ignored while analysing power consumption of modern CMPs [23, 22, 26].

In the case of modern CMPs, among all the on-chip components, cores are usually accounted for their high dynamic power consumption whereas caches are considered for their significant leakage. The heavy dynamic power of the cores are reduced by applying some classical techniques like- DVFS, DPM etc. In case of cache leakage, either state destroying or state preserving techniques are used, and in a few cases they are clubbed together. In some of the recent CMPs it has also been found that, the large on-chip LLCs increase the number of transistors with large area occupancy. This large chunk of LLC consumes heavy leakage and plays the role of a significant contributor to the total on-chip power consumption. For some recent CMPs, Table 1.1 shows the percentage contributions of on-chip caches to the total power consumption of the chip, which can motivate the researchers to reduce these numbers. This thesis focuses upon the leakage power consumption of the on-chip LLCs, which has become a limiting factor in designing modern CMPs with shrunk transistors.

| Microprocessor    | Power Consumed by on-chip Caches |

|-------------------|----------------------------------|

|                   | with respect to total power      |

| ARM 920T          | 44%                              |

| Strong ARM SA-110 | 27%                              |

| 21164 DEC Alpha   | $25	ext{-}30\%$                  |

| Niagra            | 12%                              |

| Niagra2           | 21%                              |

| Alpha 21364       | 13%                              |

| Xeon (Tulsa)      | 13%                              |

TABLE 1.1: Power consumed by on-chip caches [4, 5]

# 1.3 Thermal Issues in CMPs

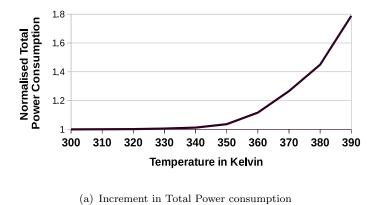

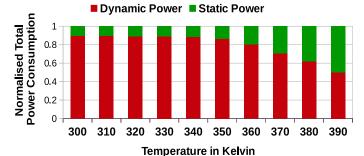

Rapid advancements in VLSI technology reduce the channel length of modern transistors, for which modern CMPs are well equipped with giant number of onchip components to enhance system performance. Increment in number of on-chip components increases the on-chip power density which in turn dissipates more heat and increases chip temperature. The raised up chip temperature quadratically increases the leakage power (ref. Equation 1.3). The increased leakage power further increases the effective chip temperature, and thus forms a circular dependency with temperature [28, 23]. However, on-chip circuitry in high temperature not only starts malfunctioning, but can also be damaged permanently. Figure 1.3 shows the change in total power consumption with the increment in chip temperature, and this increment is due to the increase in leakage power. At high temperature, leakage consumption is even as same as dynamic power. The values in the figures are collected by running the same workload with Niagara2 CMP in different temperatures in McPAT simulator [21]. The temperature values are given in Kelvin in both the figures.

#### **1.3.1** Thermal Characteristics

From the above discussion, it is pretty clear that power consumption constructs the foundation of on-chip thermal issues. Hence, as a mitigation, most of the inbuilt thermal management techniques use power consumption as an optimisation

(b) Static vs. Dynamic power

FIGURE 1.3: Power consumed by Niagara2 Chip at different temperatures.

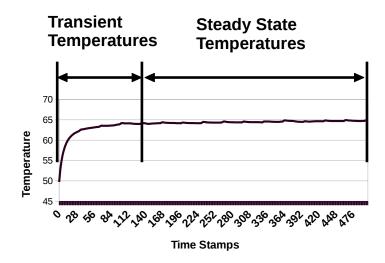

knob for thermal efficient chip design. Although the power consumption can be changed instantaneously even in practical cases, this is not true about temperature. The associated thermal capacitances of every chip element does not allow instantaneous change in temperature of the chip components. During execution the chip temperature gradually reaches its *steady-state*. The intermediate values before reaching at steady-state are known as *transient temperatures*. Figure 1.4 shows how the temperature changes over time during execution. The temperature values shown along Y-axis are in °C and X-axis represents the time stamps during execution. The values are obtained using HotSpot simulator [3].

## 1.3.2 Mitigations-at a glance

The primary objective of any thermal efficient chip design is to maintain the chip temperature under a certain value, the thermal threshold, commonly known as the critical temperature [29]. Classical chip manufacturing follows a common