Performance-Aware Test-Time Optimization Schemes for Analysis of Logic Level Faults in Channels of On-Chip Networks

Biswajit Bhowmik

#### Performance-Aware Test-Time Optimization Schemes for Analysis of Logic Level Faults in Channels of On-Chip Networks

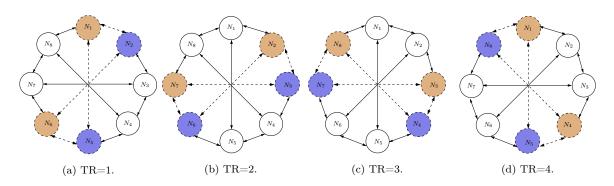

Thesis submitted in partial fulfillment of the requirements for the degree of

#### Doctor of Philosophy

by

Biswajit Bhowmik

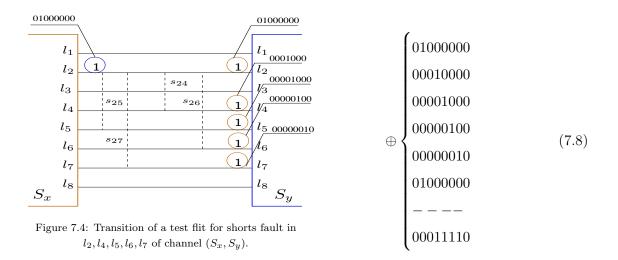

Under the supervision of

Santosh Biswas Jatindra Kumar Deka

Department of Computer Science and Engineering INDIAN INSTITUTE OF TECHNOLOGY GUWAHATI Guwahati, Assam – 781039, India April, 2018

# This Work Is Dedicated To My Mother

I Love You Maa With All My Heart...

#### Declaration

I certify that

- a. The work contained in this thesis is original and has been done by myself under the general supervision of my supervisors.

- b. The work has not been submitted to any other institute for any degree or diploma.

- c. Whenever I have used materials (data, theoretical analysis, results) from other sources, I have given due credit to them by citing them in the text of the thesis and giving their details in the references.

- d. Whenever I have quoted written materials from other sources, I have put them under quotation marks and given due credit to the sources by citing them and giving required details in the references.

Place: IIT Guwahati Date: April 29, 2018 **Biswajit Bhowmik** Research Scholar Department of Computer Science and Engineering Indian Institute of Technology Guwahati Guwahati, Assam - 781039, India

#### CERTIFICATE

This is to certify that the thesis entitled "Performance-Aware Test-Time Optimization Schemes for Analysis of Logic Level Faults in Channels of On-Chip Networks" being submitted by Mr. Biswajit Bhowmik to the Department of Computer Science and Engineering, Indian Institute of Technology Guwahati, is a record of bona fide research work under our supervision and is worthy of consideration for the award of the degree of Doctor of Philosophy of the Institute.

The results contained in this thesis have not been submitted in part or full to any other university or institute for the award of any degree or diploma.

Place: IIT Guwahati Date: April 29, 2018 Prof. Jatindra Kumar DekaProfessorDept. of Computer Sc. and Engg.Indian Institute of Technology GuwahatiGuwahati, Assam - 781039, India

Place: IIT Guwahati Date: April 29, 2018

#### Abstract

Today manycore, multiprocessor systems-on-chip (MPSoCs) have been introduced to cope with the growing demand for high-speed communication requirements of intensive-computing applications. However, in spite of rapid advancements in deep-submicron (DSM) technology and the seamless integration of intellectual property (IP) modules in the SoCs, these busbased interconnection architectures have become unable to meet the performance requirements - bandwidth, throughput, latency, power, etc. in the applications where high-performance computation and communication is the dominant consideration. In other words, such SoCs often fail to sustain high-volume computation and high-speed communication among their components due to the use of global buses as the interconnects. The network-on-chip (NoC) as an alternate prevalent interconnection infrastructure has been continuously occupying the space of the SoC. An NoC comprises a large number of IP cores, routers, and high-speed channels (interconnects) that construct a structure (topology) spanning across the chip. However, aggressive CMOS scaling expedites interconnect and transistor wear-out, shortening the lifespan of these basic components which are often vulnerable to a number of manufacturing and transient faults due to aging, physical defects, or hostile attacks invoked by malicious third parties. For instance, basic classical logic level faults treated as the manufacturing faults, such as stuck-at, open, and shorts in NoC channels cause various system-level failures and subsequent degradation of reliability, yield, and performance of the computing platform. One approach to tackle channel-faults in NoCs is to replace the faulty channel-wires with spare wires. Such scheme is not cost-effective as the area overhead is substantially increased. Another approach is to exercise a fault-tolerant routing algorithm that directs traffic (application data packets) over channels by avoiding the faulty wires or an alternative fault-free path in order to connect the source and destination nodes, keeping the NoC functional. However, most of the fault-tolerant schemes do not consider any test mechanism for channels. One prerequisite of these approaches includes the knowledge about the health status of the channels which can only be inferred by an effective test method. Most of the commonly practiced approaches acknowledge numerous disadvantages in terms of test issues like high test volume, high silicon area overhead, high test time, low fault coverage, and lack of scalability.

This dissertation pursues efficient self-test approaches for manufacturing faults including a little emphasis on the transient faults and other logic level faults, e.g., packet deadlock, in the NoC channels in order to improve the yield and reliability in NoC-based communication systems. The main goal of this dissertation is to develop an environment for the test-time minimization problem in addition to associated issues, such as test area overhead, performance overhead at the runtime, etc. In order to reduce the test cost in terms of low test time, low area overhead, low-performance overhead, etc., the proposed test approach is divided into two parts: test algorithm and test scheduling. As the first pillar towards the goal, an on-line, distributed built-in-self-test (BIST) oriented test algorithm is proposed, that with the help of a test module (must be included in a modern NoC) has the capability in detecting a channel fault and identifying the faulty wires from the channel. As the second pillar to reach the goal, a suitable test scheduling scheme is proposed, which makes the present test solution scalable with respect to different network architectural characteristics: network size, channel width, and network type, i.e., large-scale NoC architectures in general. This dissertation contains five contributed works. First three contributions explore the test of stuck-at, open, and short faults in NoC channels. Here, the channels are assumed to follow the single fault model. The fourth contribution includes the test of manufacturing and transient faults in the channels. The final contribution includes the test of coexistent manufacturing channel-faults. In the last two contributions, a channel can be assumed to follow the multiple fault model. In all the contributions, experimental results reveal that the proposed solutions impose less test time, area, and performance overhead as compared to existing testing techniques.

#### Acknowledgments

First and foremost, I would like to convey my deepest gratitude and prayer to my mother, whose love, care, bless, support, inspiration, and sacrifice have made my success possible, provide me the liberty to be fearless and explore new things in life.

With a sense of adoration, I do express many thanks and a lot of love to Sovana who always guided me in the proper way, and grew interests in life. I cannot forget her continuous encouragements that keep me energetic. Probably, I would have never decided to pursue a PhD without her encouragement. Without her devotion and effort, it would also become very difficult to complete the thesis in time.

Especially, I would like to be evidence for my honor to Dr. Rabindranath Bhowmik (Sejda), Assistant Professor, Department of Physics, University of Pondicherry, and Mr. Pradip Kumar Maity (my favorite Pradipda) who put the first brick in building my career, and helped and supported me by all the ways to become what I am at present.

I would like to express my special appreciation and thanks to my supervisors, Prof. Santosh Biswas and Prof. Jatindra Kumar Deka, whose joy and enthusiasm, selfless time and care, meticulous and contagious attention helped me to grow as a researcher. This thesis is a culmination of a perfect working relationship with my supervisors. Their brilliant advice and constant supports towards a quality research as well as on my career always remain priceless.

With profound glee, I extend my special thanks to Prof. Bhargab B. Bhattacharya, Advanced Computing and Microelectronics Unit, Indian Statistical Institute Kolkata, India – 700108, who provided me immense support during my journey towards PhD, and generously paved the way for my development as a research scientist. I am very grateful to him for sharing his knowledge and novel ideas with me and bearing his valuable time towards preparing my research manuscripts.

I am also highly grateful to my Doctoral Committee members, Prof. Diganta Goswami, Prof. Arnab Sarkar, Prof. Partha Sarathi Mandal for sharing their insightful comments and suggestions on my research work. I express my sincere thanks to Prof. Sukumar Nandi, Prof. Hemangee K. Kapoor, Dr. Deepanjan Kesh, Dr. Sushanta Karmakar, Prof. Purandar Bhaduri, Dr. V. Vijaya Saradhi, Dr. Arijit Sur, Dr. T. Venkatesh, Prof. Pinaki Mitra, Prof. Gautam Barua, Prof. S. V. Rao, Dr. Benny George K, and other faculty members of the Department of Computer Science and Engineering, for providing a nice research environment in the department, and support my research works in many ways. I also thank department's Technical Officers Mr. Bhriguraj Bora and Mr. Nanu A. Kachari, Technical Superintendents Raktajit Pathak, Nava Kumar Boro, and Pranjit Talukdar, and Administrative Staffs Monojit Bhattacharjee, Gauri Khuttiya Deori, and Prabin Bharali for extending their helping hands in solving many issues which I faced during my PhD.

I cherished my stay in the institute largely due to my friends. I thank Niladri Sett, Chandan Kalita, Sandip Chakraborty, Pradeep Kumar Biswal, Subhrendu Chattopadhyay, Rahul Gangopadhyay, Shirshendu Das, Shounak Chakraborty, Mayank Naresh Agarwal, Shuvendu Rana, Sibaji Gaj, Satish Kumar, Awnish Kumar, Mrityunjay Singh, Madhusudan Paul, Rajesh Devraj, Durgesh Kumar, Mousum Handique, Parikshit Saikia, Lalatendu Behera, Ranajit Senko, Manas Kumar Panda, Amit Kumar Srivastava, Kunwer Mrityunjay Singh, Sanjit Kumar Roy, Manojit Ghose, Pradeep Kumar Sharma, Rakesh Pandey, Sukarn Agarwal, Piyoosh Purushothaman Nair, Sangeet Saha, Akash Anil, Subrata Tikadar, Nagaraj Adiga, Bidisha Sharma, Shrestha Tripathy, and many others for their support, encouragement, and delightful company. I am also thankful to Nikhil Bandhu Pal, Graphite India Ltd., Durgapur, and my colleagues and friends of Bengal College of Engineering and Technology Durgapur, West Bengal-713212, who encouraged me to pursue this PhD.

The development of this thesis would not have been possible without financial support from the MHRD, Govt. of India. I would also like to thank the Ministry of Electronics and Information Technology (Meity), Govt. of India for financial support from the budget of the sponsored project titled "On-Line Testing of Complex VLSI Circuits using Failure Detection and Diagnosis Theory of Discrete Event Systems" to publish my research papers in many prestigious international conferences and after the tenure of my MHRD fellowship was over.

Lastly, I express my deepest worship to "Eswar", the supernatural being worshiped by people, and nature, where the basic source of my life energy resides: words cannot express how grateful I am.

Before I finish, I would like to share that when one writes a research article and thesis then he realizes the true power of the Latex and MS-Word from grammar checks to replace all. Simply, without this software as a document preparation system, this thesis would not possibly be written. Thanks to the American computer scientist Prof. Leslie Lamport, and the Philanthropist Bill Gates and his Microsoft Corporation!

Place: IIT Guwahati Date: April 29, 2018

**Biswajit Bhowmik**

### Contents

| Li       | st of | Figures                            |  |   |   |   | xi   |

|----------|-------|------------------------------------|--|---|---|---|------|

| Li       | st of | Tables                             |  |   |   |   | xix  |

| Li       | st of | Abbreviations and Symbols          |  |   |   | x | xiii |

| 1        | Intr  | oduction                           |  |   |   |   | 1    |

|          | 1.1   | Introduction                       |  | • |   |   | 1    |

|          | 1.2   | SoC Integration and Its Challenges |  | • | • |   | 2    |

|          | 1.3   | SoC to NoC: A Paradigm Shift       |  |   | • |   | 2    |

|          | 1.4   | Research on NoC Architectures      |  |   | • |   | 3    |

|          | 1.5   | Necessity of NoC Channel Testing   |  |   |   | • | 4    |

|          | 1.6   | Literature Review                  |  |   |   | • | 5    |

|          | 1.7   | Research Overview                  |  |   |   | • | 8    |

|          | 1.8   | Motivation and Problem Formulation |  | • | • |   | 9    |

|          | 1.9   | Major Contributions of the Thesis  |  | • | • |   | 10   |

|          | 1.10  | Organization of the Thesis         |  |   | • | • | 11   |

| <b>2</b> | Lite  | erature Survey                     |  |   |   |   | 13   |

|          | 2.1   | Introduction                       |  |   |   |   | 13   |

|          | 2.2   | NoC Basics                         |  |   |   |   | 14   |

|          |       | 2.2.1 IP Cores                     |  |   | • |   | 15   |

|          |       | 2.2.2 Routers                      |  |   | • |   | 17   |

|          |       | 2.2.3 Communication Channels       |  |   |   |   | 21   |

|          | 2.3   | NoC Topology                       |  |   |   |   | 23   |

|          |       | 2.3.1 Regular Topology             |  |   | • |   | 24   |

|          |       | 2.3.2 Irregular Topology           |  |   |   |   | 26   |

|   | 2.4 | Fault Modeling $\ldots \ldots 26$ |

|---|-----|------------------------------------------------------------------------------------------------------------------------------|

|   |     | 2.4.1 Sources of Faults                                                                                                      |

|   |     | 2.4.2 Basic Fault Models                                                                                                     |

|   |     | 2.4.3 Types of Testing                                                                                                       |

|   | 2.5 | Testing of NoC Faults                                                                                                        |

|   |     | 2.5.1 Types of Test Modes                                                                                                    |

|   |     | 2.5.2 Test of NoC Building Blocks                                                                                            |

|   | 2.6 | Literature Review: Test of Communication Channels                                                                            |

|   |     | 2.6.1 Quality of Service                                                                                                     |

|   |     | 2.6.2 Network Performance                                                                                                    |

|   |     | 2.6.3 Reliability and Yield Improvement Issues                                                                               |

|   |     | 2.6.4 Testing of Transient Faults in Channels                                                                                |

|   |     | 2.6.5 Testing of Manufacturing Faults in Channels                                                                            |

|   | 2.7 | Issues Related to Prior Works                                                                                                |

|   | 2.8 | Motivation and Contribution                                                                                                  |

|   | 2.9 | Conclusion                                                                                                                   |

| 3 | ۸dd | dressing Stuck-at Faults in Channels of Networks-on-Chip 65                                                                  |

| J | 3.1 | Introduction                                                                                                                 |

|   | 3.2 | Motivation and Contributions                                                                                                 |

|   | 3.3 | SAFs and System Level Failures                                                                                               |

|   | 0.0 | 3.3.1         SAF Model         68                                                                                           |

|   |     | 3.3.2         System Level Failures         70                                                                               |

|   | 3.4 | Proposed Test Model                                                                                                          |

|   | 0.1 | 3.4.1 Test Infrastructure for SAFs                                                                                           |

|   |     | 3.4.2 Testing SAFs in Channels of a Node                                                                                     |

|   | 3.5 |                                                                                                                              |

|   | 0.0 | Test Scheduling       75         3.5.1       Finding Test Rounds and Iterations       76                                     |

|   |     | 3.5.2 Determination of Test Time                                                                                             |

|   | 3.6 | Experimental Results                                                                                                         |

|   | 5.0 | 3.6.1 Test Area Overhead                                                                                                     |

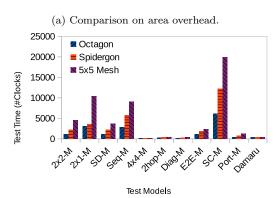

|   |     | 3.6.2       Test Clock Cycles       83                                                                                       |

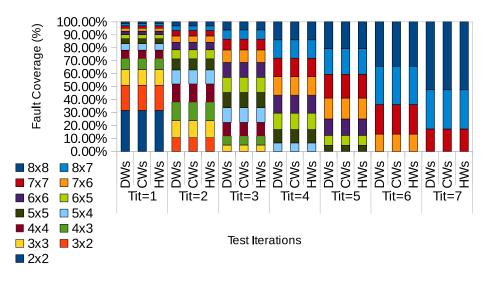

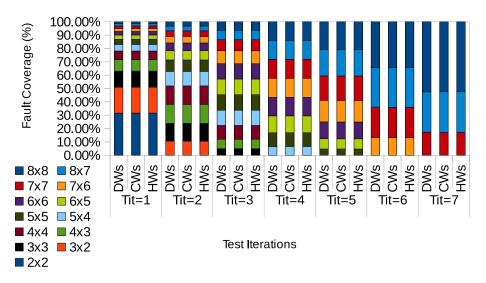

|   |     | 3.6.3 Link and Fault Coverage Metrics                                                                                        |

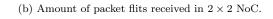

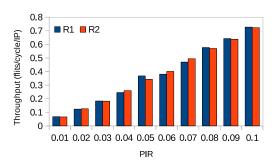

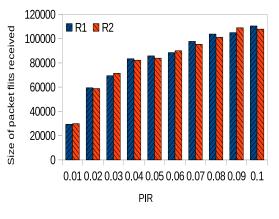

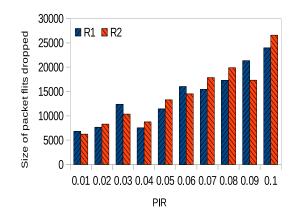

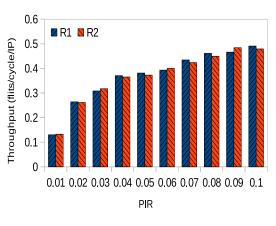

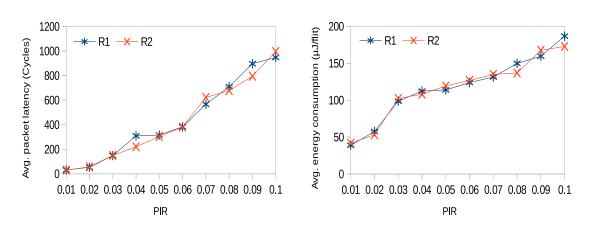

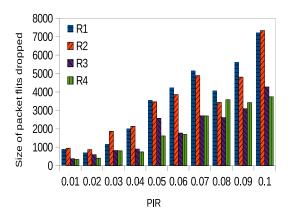

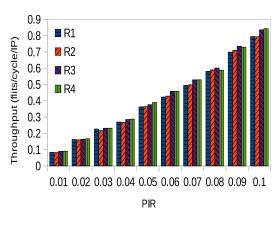

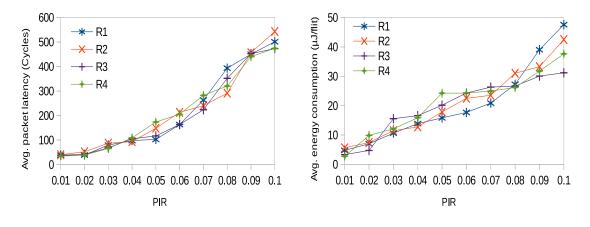

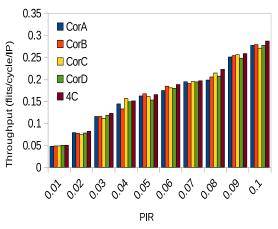

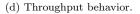

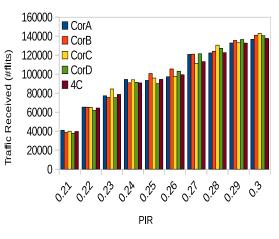

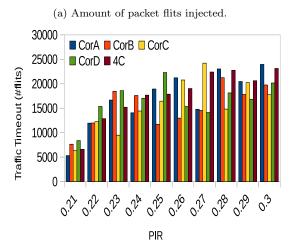

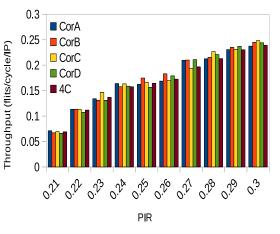

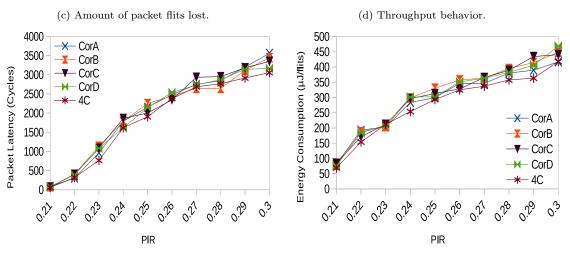

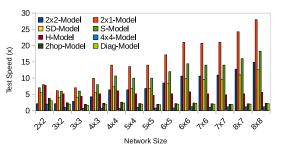

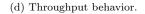

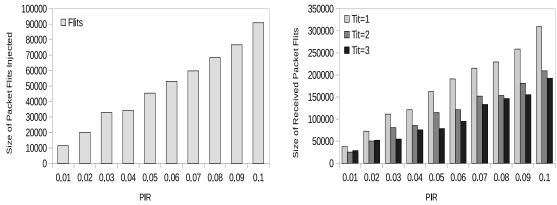

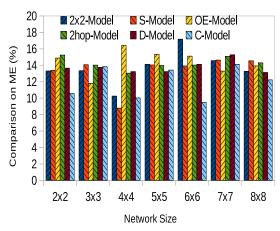

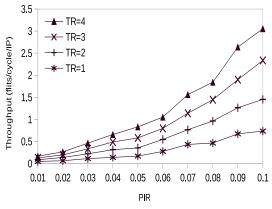

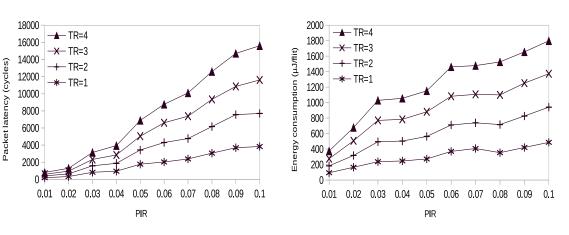

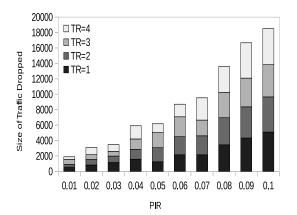

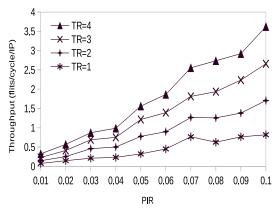

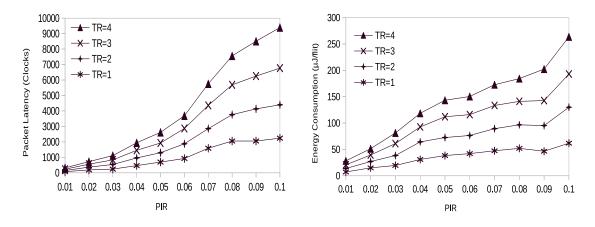

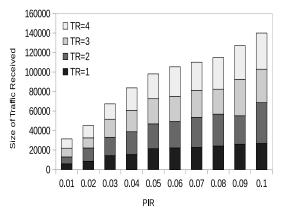

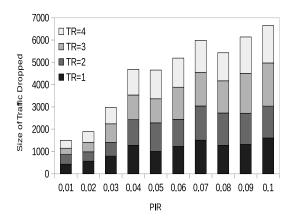

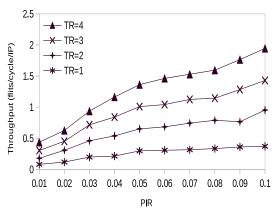

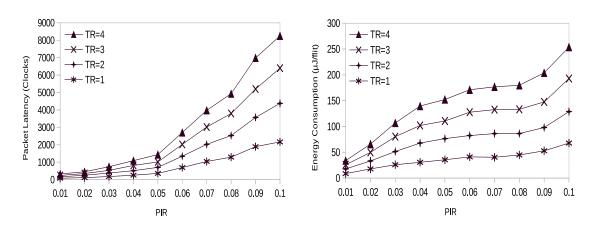

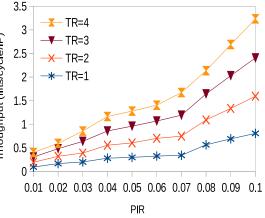

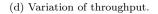

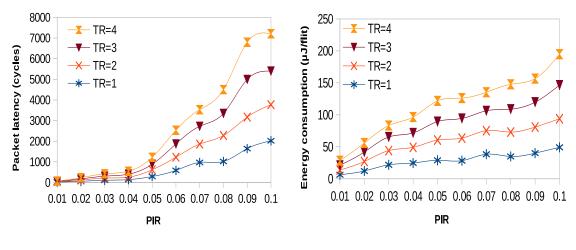

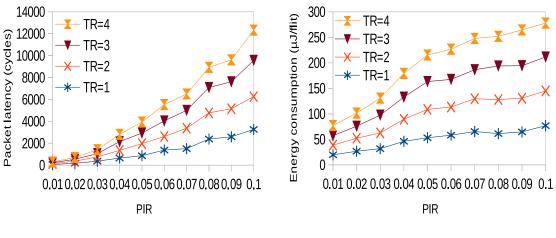

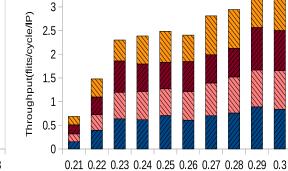

|   |     | 3.6.4       Network Performance Metrics       86                                                                             |

|   | 3.7 | Solution Scalability                                                                                                         |

|   | J.1 |                                                                                                                              |

|   |     |                                                                                                                              |

|   | 20  | 3.7.2 Scalability with Channel Width                                                                                         |

|   | 3.8 | Solution Portability                                                                                                         |

|   | 3.9          | Benefi | its over Prior Works                          | 99  |

|---|--------------|--------|-----------------------------------------------|-----|

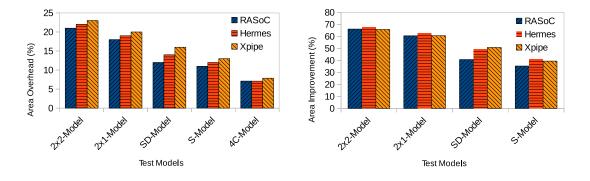

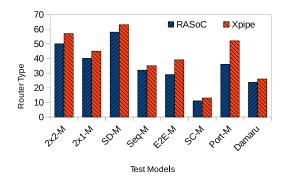

|   |              | 3.9.1  | Benefits in Hardware Area Overhead            | 100 |

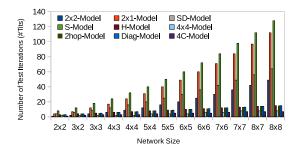

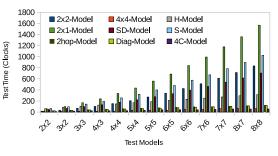

|   |              | 3.9.2  | Benefits in Test Time                         | 101 |

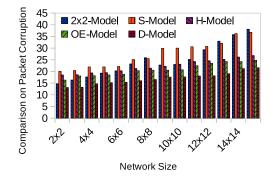

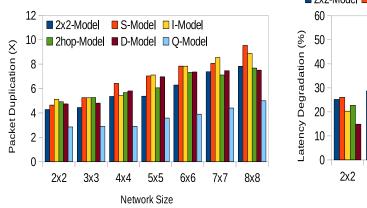

|   |              | 3.9.3  | Benefits in Channel Errors                    | 103 |

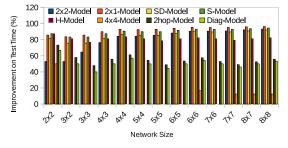

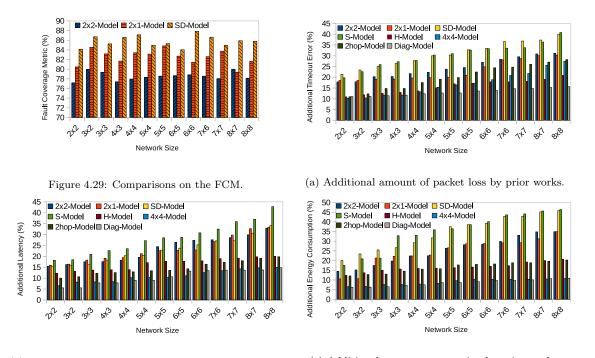

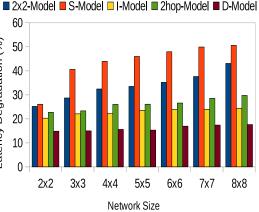

|   |              | 3.9.4  | Benefits in Performance Overhead              | 104 |

|   | 3.10         | Limita | ations                                        | 105 |

|   | 3.11         | Conclu | usion                                         | 106 |

| 4 | Max          |        |                                               | 107 |

|   | 4.1          |        | luction                                       | 107 |

|   | 4.2          | Backg  | round                                         | 109 |

|   | 4.3          | Motiv  | ation, Problem Formulation, and Contributions | 110 |

|   | 4.4          | At-Sp  | eed Test Mechanism                            | 112 |

|   |              | 4.4.1  | Open Fault Model                              | 113 |

|   |              | 4.4.2  | Packet Dropping: A System Level Failure       | 115 |

|   |              | 4.4.3  | Test Infrastructure                           | 116 |

|   |              | 4.4.4  | Testing of Opens in Channels from a Node      | 117 |

|   | 4.5          | Test S | Scheduling                                    | 120 |

|   |              | 4.5.1  | Determination of Corner Nodes                 | 120 |

|   |              | 4.5.2  | The 4-Corner Principle                        | 123 |

|   |              | 4.5.3  | Computation of Test Iterations and Time       | 126 |

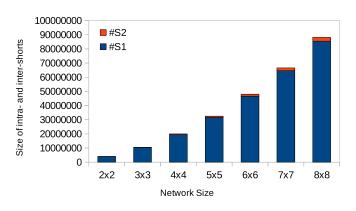

|   | 4.6          | Simula | ation Results                                 | 128 |

|   |              | 4.6.1  | Silicon Area Evaluation                       | 129 |

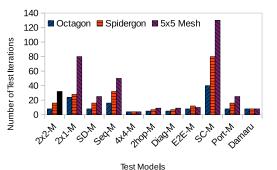

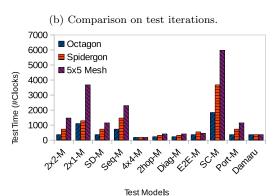

|   |              | 4.6.2  | Test Iteration and Time Evaluation            | 130 |

|   |              | 4.6.3  | Test and Fault Coverage Evaluation            | 131 |

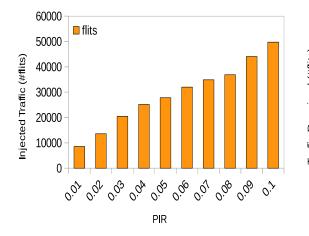

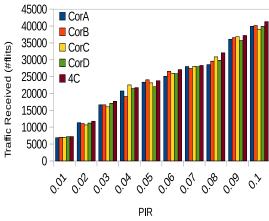

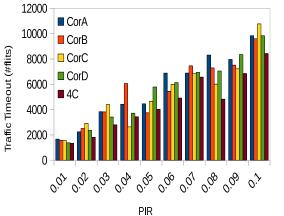

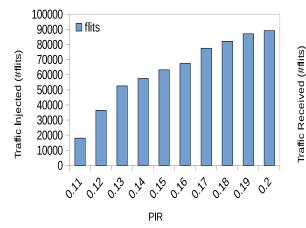

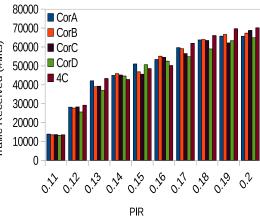

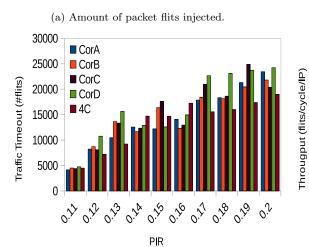

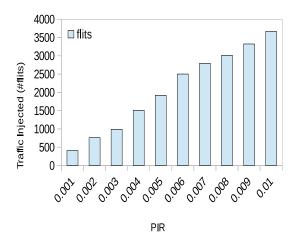

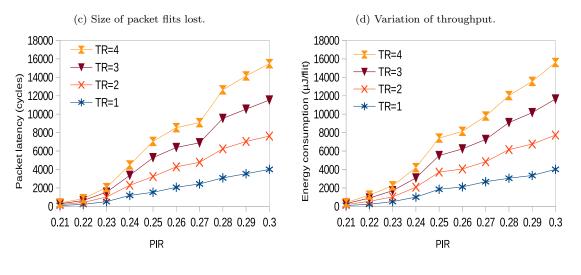

|   |              | 4.6.4  | On-Line Performance Evaluation                | 133 |

|   | 4.7          | Soluti | on Scalability                                | 136 |

|   |              | 4.7.1  | Scaling with Channel Width                    | 136 |

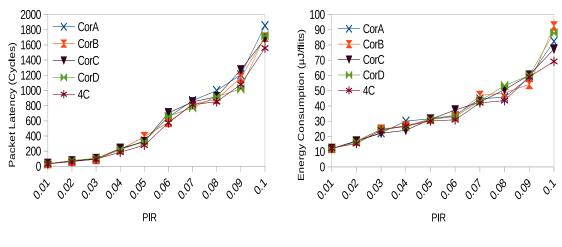

|   |              | 4.7.2  | Scaling with Network Size                     | 140 |

|   | 4.8          | Soluti | on Portability                                | 143 |

|   | 4.9          |        | arison Study                                  | 145 |

|   |              | 4.9.1  | Comparison on Hardware Area Overhead          | 147 |

|   |              | 4.9.2  | Comparison on Test Iterations and Time        | 148 |

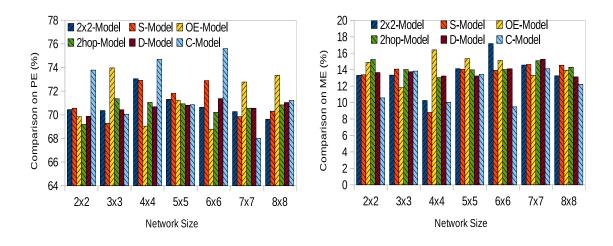

|   |              | 4.9.3  | Comparison on Coverage Metrics                | 149 |

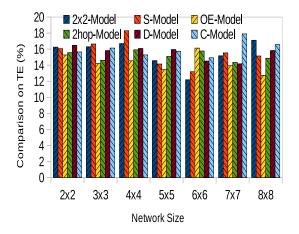

|   |              | 4.9.4  | Comparison on Performance Overhead            | 150 |

|   | 4.10         |        | ations                                        | 152 |

|   |              |        | usion                                         | 152 |

|   | <b>T T T</b> | CONCI  |                                               | 104 |

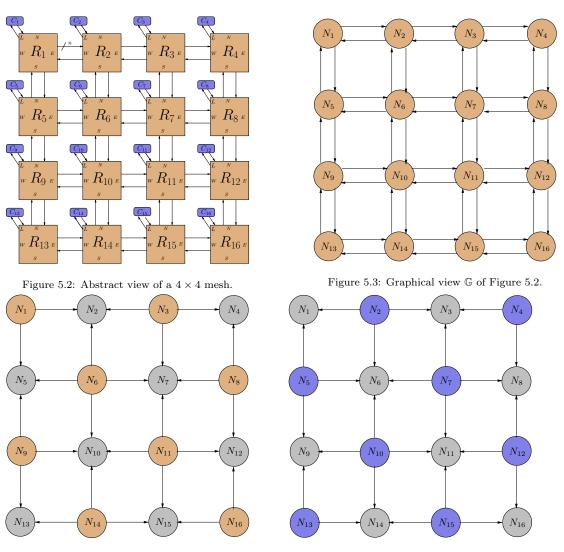

| <b>5</b> | Imp  | act of Short-Channel Faults in On-Chip Interconnection Networks 1 | 155 |

|----------|------|-------------------------------------------------------------------|-----|

|          | 5.1  | Introduction                                                      | 155 |

|          | 5.2  | Motivation, Problem Formulation, and Contributions                | 156 |

|          | 5.3  | Cluster Formation                                                 | 158 |

|          | 5.4  | Network Failures due to Channel-Shorts                            | 160 |

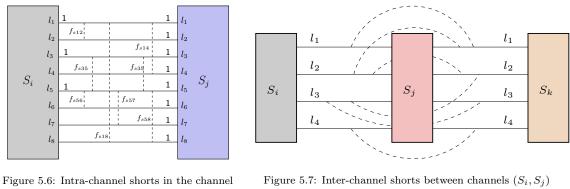

|          | 5.5  | Short-Channel Fault Model                                         | 162 |

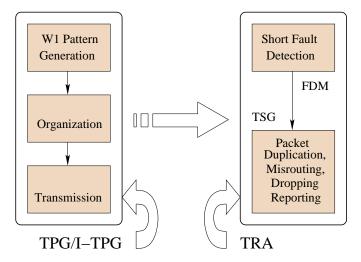

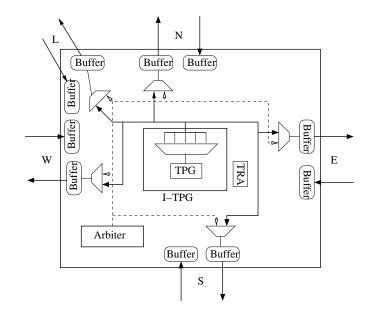

|          | 5.6  | Test Architecture and Packet Format for Fault Detection           | 163 |

|          | 5.7  | Testing of Channel-Shorts at a Node                               | 166 |

|          |      | 5.7.1 Fault Detection                                             | 166 |

|          |      | 5.7.2 Fault Diagnosis                                             | 167 |

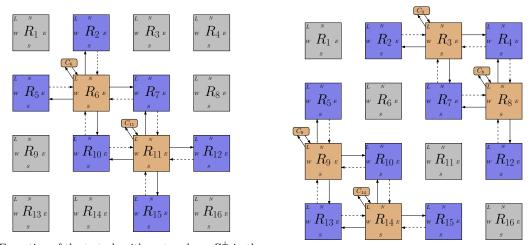

|          | 5.8  | Test Scheduling                                                   | 168 |

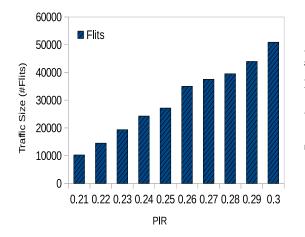

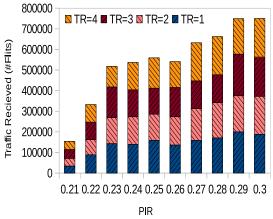

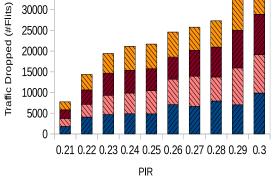

|          | 5.9  | Results                                                           | 171 |

|          |      | 5.9.1 Simulation Setup                                            | 171 |

|          |      | 5.9.2 Area Overhead                                               | 173 |

|          |      | 5.9.3 Test Clocks and Coverage Metrics Evaluation                 | 173 |

|          |      | 5.9.4 Performance Evaluation                                      | 174 |

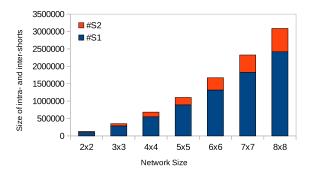

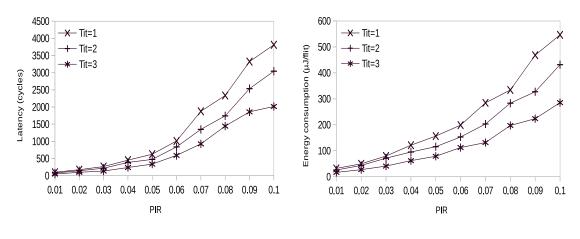

|          | 5.10 | Method Scalability                                                | 176 |

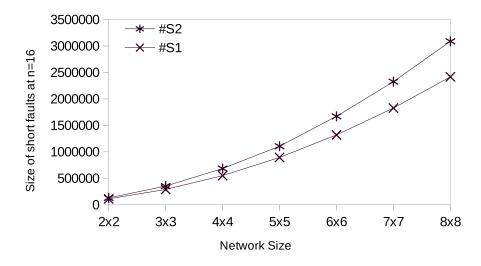

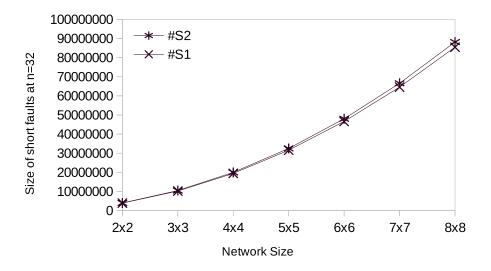

|          |      | 5.10.1 Scalability with NoC Size                                  | 176 |

|          |      | 5.10.2 Scalability with Channel Width                             | 179 |

|          | 5.11 | Method Adaptability                                               | 182 |

|          | 5.12 | Comparative Study                                                 | 185 |

|          |      | 5.12.1 Benefits in Area Overhead                                  | 185 |

|          |      | 5.12.2 Benefits in Test Clocks                                    | 186 |

|          |      | 5.12.3 Benefits in Performance Overhead                           | 187 |

|          | 5.13 | Limitations                                                       | 189 |

|          | 5.14 | Conclusion                                                        | 190 |

| 6        | АТ   | est Time and Energy Optimized Scheme for On-Chip Channel-Faults 1 | 191 |

|          | 6.1  | Introduction                                                      | 191 |

|          | 6.2  | Motivation, Problem Formulation, and Contributions                | 193 |

|          | 6.3  | Proposed Test Mechanism                                           | 195 |

|          |      | 6.3.1 Testing of Channel-Shorts From a Node                       | 195 |

|          |      | 6.3.2 Detection of Other Types of Channel-Faults                  | 199 |

|          | 6.4  |                                                                   | 201 |

|          |      | -                                                                 | 201 |

|          |      | -                                                                 | 202 |

|          |      |                                                                   | 203 |

|          |      |                                                                   | 205 |

|          |      |                                                                   |     |

|   | 6.5        | Simula         | ation Results                                                          | 206               |

|---|------------|----------------|------------------------------------------------------------------------|-------------------|

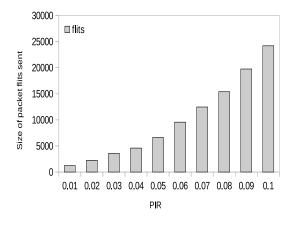

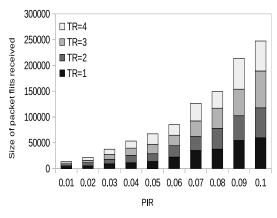

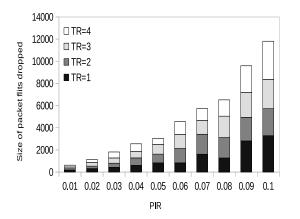

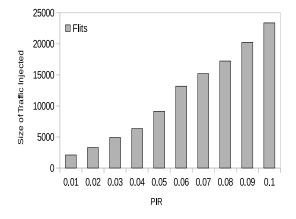

|   |            | 6.5.1          | Simulation Setup                                                       | 207               |

|   |            | 6.5.2          | Hardware Area Overhead                                                 | 208               |

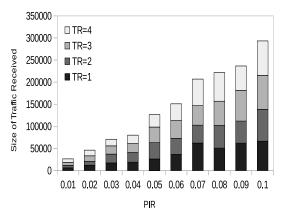

|   |            | 6.5.3          | Solution Evaluation                                                    | 209               |

|   | 6.6        | Solutio        | on Scalability                                                         | 213               |

|   |            | 6.6.1          | With NoC Size                                                          | 213               |

|   |            | 6.6.2          | With Channel Width                                                     | 216               |

|   | 6.7        | Solutio        | on Adaptability                                                        | 219               |

|   | 6.8        | Compa          | arative Study                                                          | 221               |

|   |            | 6.8.1          | Benefits in Area Overhead                                              | 223               |

|   |            | 6.8.2          | Benefits in Test Clocks                                                | 223               |

|   |            | 6.8.3          | Benefits in Coverage Metrics and Channel Errors                        | 225               |

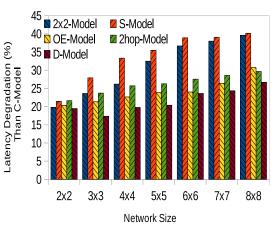

|   |            | 6.8.4          | Benefits in Performance Overhead                                       | 225               |

|   | 6.9        | Limita         | tions                                                                  | 228               |

|   | 6.10       | Conclu         | ision                                                                  | 229               |

| - |            | ·1 T           |                                                                        | 0.0.1             |

| 7 | Орt<br>7.1 |                | Detection and Diagnosis of Coexistent On-Chip Channel-Faults<br>uction | <b>231</b><br>231 |

|   | 7.1<br>7.2 |                | ation and Contribution                                                 | 231<br>232        |

|   | 7.2        |                | sed Test Model                                                         | 232<br>234        |

|   | 6.)        | 7.3.1          |                                                                        | 234<br>234        |

|   |            | 7.3.1<br>7.3.2 | Coexistent Short and Stuck-at Fault Model                              |                   |

|   |            |                | Test Module and Packet Format                                          | 237               |

|   |            | 7.3.3          | Testing of CSSAFs in Channels                                          | 238               |

|   | 7 4        | 7.3.4          | Non-diagnosable Faults                                                 | 242               |

|   | 7.4        |                | cheduling                                                              | 242               |

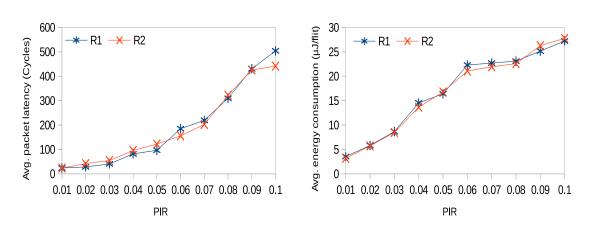

|   |            | 7.4.1          | Scheduling Nodes                                                       | 243               |

|   |            | 7.4.2          | Test Time Evaluation                                                   | 245               |

|   | 7.5        |                | ation Results                                                          | 246               |

|   | 7.6        |                | on Scalability                                                         | 252               |

|   | 7.7        |                | on Adaptability                                                        | 258               |

|   | 7.8        |                | ts Gained                                                              | 261               |

|   |            | 7.8.1          | Test Area Benefits                                                     | 261               |

|   |            | 7.8.2          | Test Time Benefits                                                     | 262               |

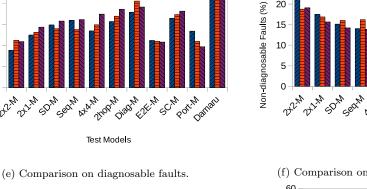

|   |            | 7.8.3          | Fault Coverage Benefits                                                | 264               |

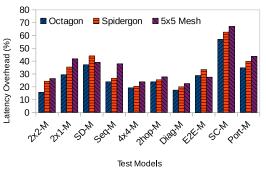

|   |            | 7.8.4          | Performance Benefits                                                   | 265               |

|   | 7.9        | Conclu         | usion                                                                  | 265               |

| 8   | Summary and Future Works |                          |     |  |  |  |  |

|-----|--------------------------|--------------------------|-----|--|--|--|--|

|     | 8.1                      | Summary of Contributions | 267 |  |  |  |  |

|     | 8.2                      | Future Works             | 269 |  |  |  |  |

|     | 8.3                      | Concluding Remarks       | 274 |  |  |  |  |

| Bi  | Bibliography             |                          |     |  |  |  |  |

| Lis | List of Publications     |                          |     |  |  |  |  |

| Aι  | Author's Brief-Biography |                          |     |  |  |  |  |

# List of Figures

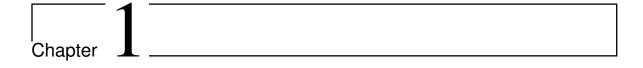

| High level view of an NoC paradigm                                                       | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

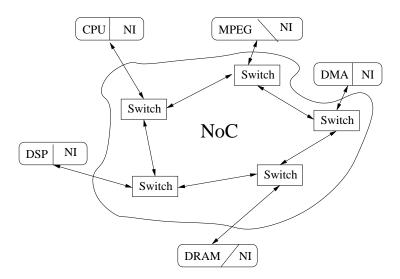

| Various IP cores in a Microcontroller-based system on a chip                             | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

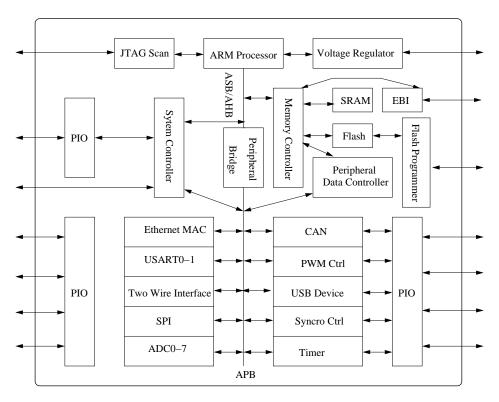

| General architectural view of an NoC router with its main components. $\ldots$           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

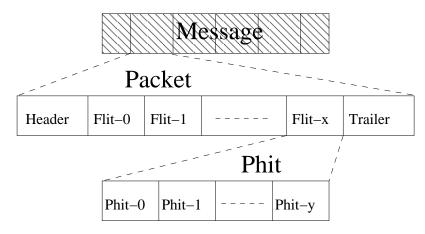

| An NoC message organization.                                                             | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

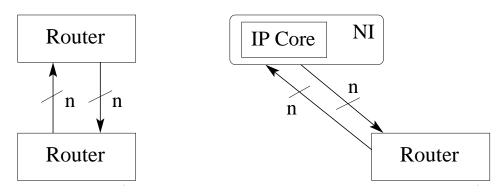

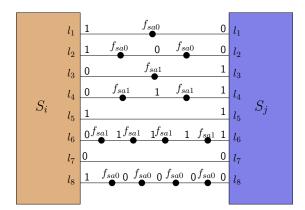

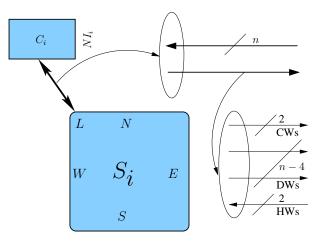

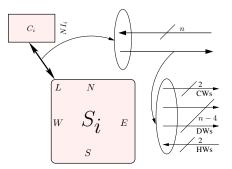

| Abstract representation of a communication channel in an NoC                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

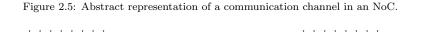

| Bidirectional and unidirectional channel wires from the output ports of a router         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $S_i$                                                                                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

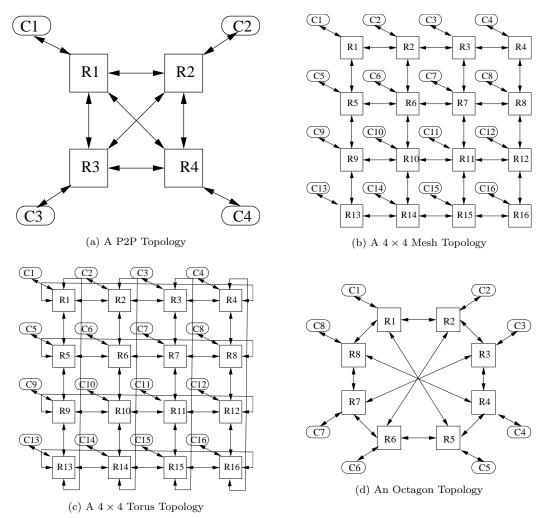

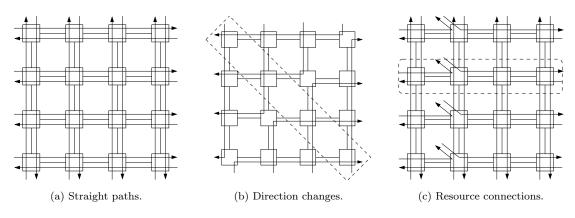

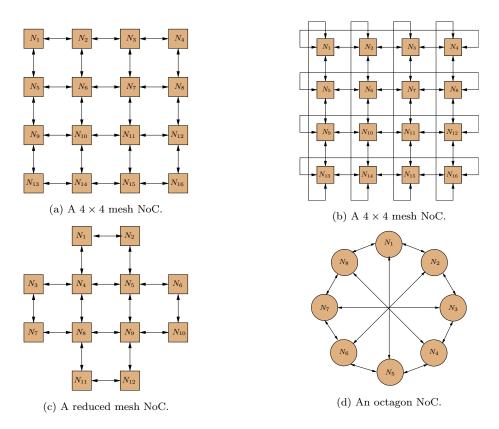

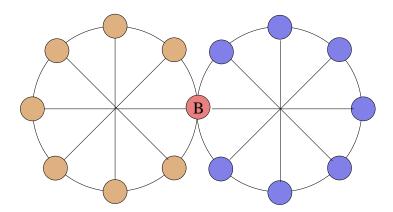

| High level view of NoCs with direct topologies.                                          | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

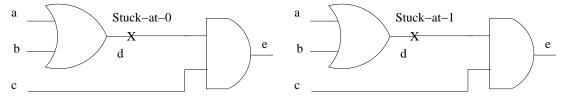

| An example of the SSA fault model.                                                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

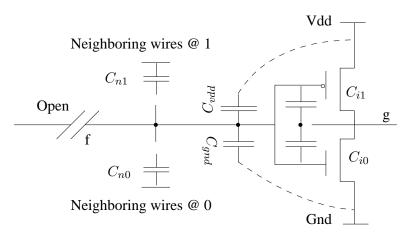

| Transistor level fault model for open defects                                            | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

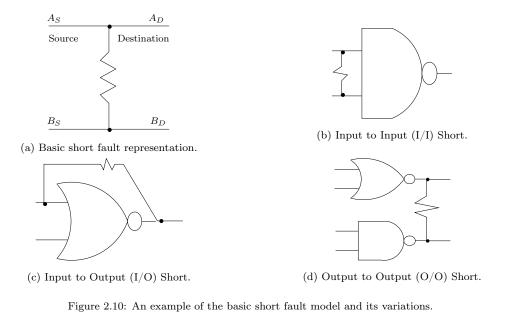

| An example of the basic short fault model and its variations. $\ldots$ $\ldots$ $\ldots$ | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

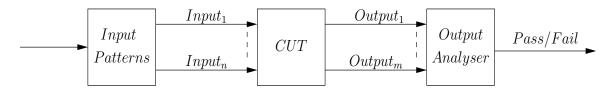

| Basic Testing Approach of a VLSI Circuit.                                                | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

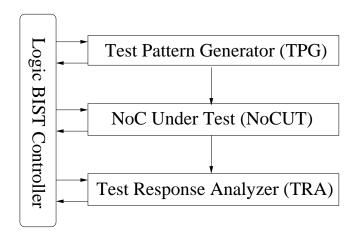

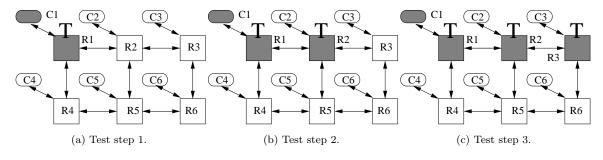

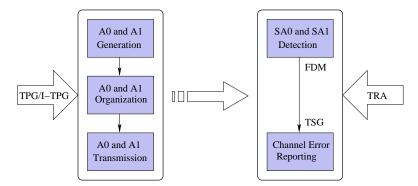

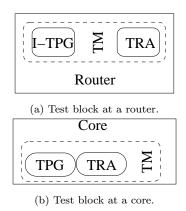

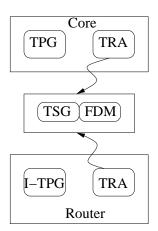

| Basic built-in-self-test scheme for an NoC under test                                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

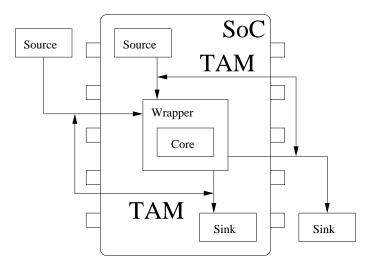

| Conceptual architecture for testing of cores                                             | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

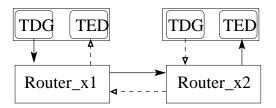

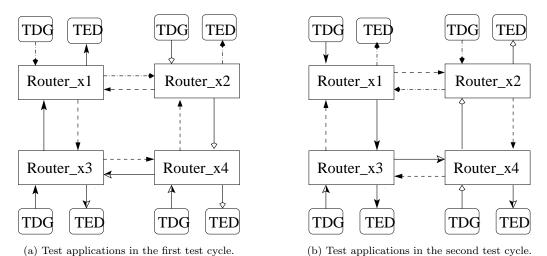

| Test configurations in first functional-based router testing                             | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Second functional-based router testing                                                   | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Progressive router testing                                                               | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Partial scan-based router testing                                                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BISTed deflective router testing phases                                                  | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

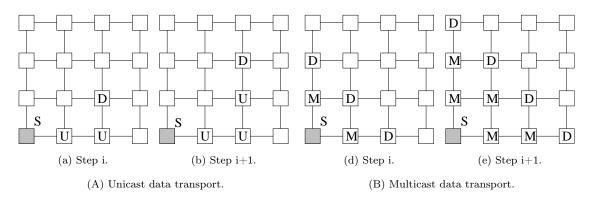

| Unicast and multicast based test schemes for router blocks in a NoC. S: source;          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D: destination; U: routers in unicast mode; M: routers in multicast mode. $\ .$ .        | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

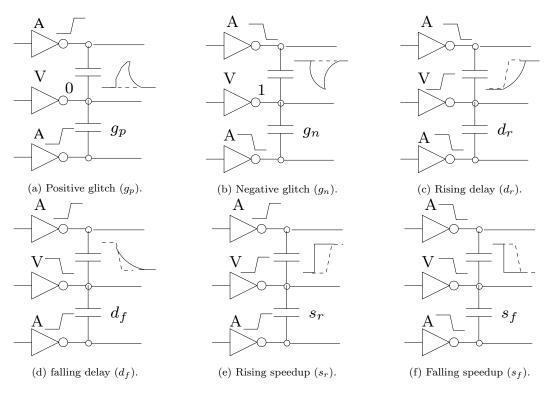

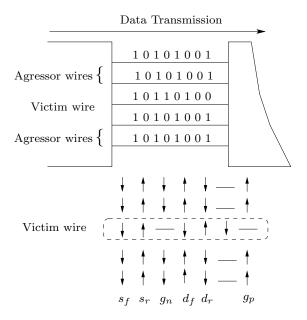

| The maximal aggressor fault model for different states of a crosstalk fault. A           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| and V represent a aggressor and victim wire, respectively. $\ldots$ . $\ldots$ .         | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Optimize test sequence for the MAF model                                                 | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

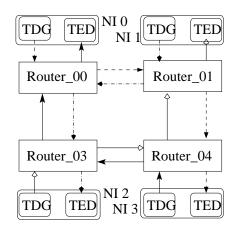

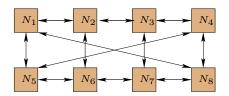

| The $2 \times 2$ neighborhood-based test configuration                                   | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

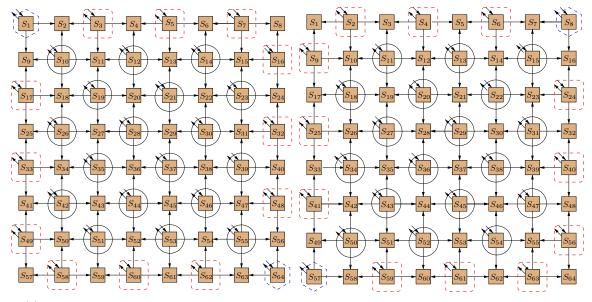

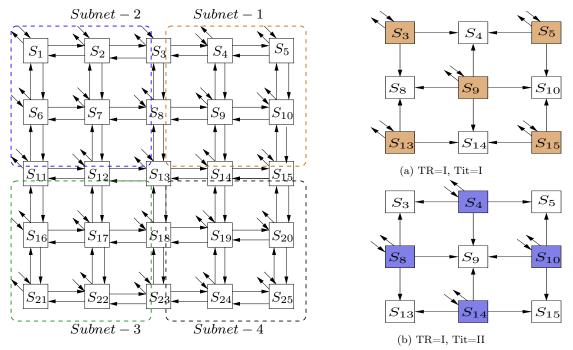

| Concurrent application of $2\times 2$ test configurations on a $4\times 4$ mesh network  | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                          | General architectural view of an NoC router with its main components.An NoC message organization.Abstract representation of a communication channel in an NoC.Bidirectional and unidirectional channel wires from the output ports of a router $S_i$ .High level view of NoCs with direct topologies.An example of the SSA fault model.Transistor level fault model for open defects.An example of the basic short fault model and its variations.Basic Testing Approach of a VLSI Circuit.Basic built-in-self-test scheme for an NoC under test.Conceptual architecture for testing of cores.Test configurations in first functional-based router testing.Progressive router testing.Progressive router testing.Basic and multicast based test schemes for router blocks in a NoC. S: source;D: destination; U: routers in unicast mode; M: routers in multicast mode.The maximal aggressor fault model for different states of a crosstalk fault. Aand V represent a aggressor and victim wire, respectively.Optimize test sequence for the MAF model.The 2 × 2 neighborhood-based test configuration. |

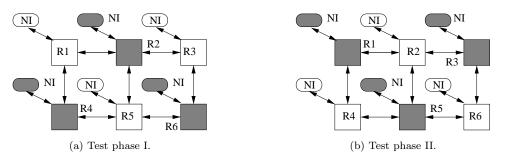

| 2.24 | The $2 \times 1$ neighborhood-based test configuration                                        | 51 |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.25 | Concurrent test application of $2 \times 1$ test configurations on the $2 \times 2$ neighbor- |    |

|      | hood. Channels denoted by gray color remain unused in a test cycle                            | 52 |

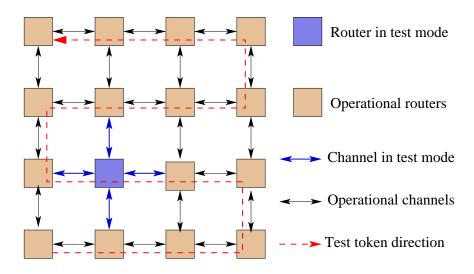

| 2.26 | Sequentially one router selection method for the on-line testing of channels on               |    |

|      | a $4\times 4$ mesh network. Each router which gets a token can start testing itself           |    |

|      | with the help of its neighbors. Only one router and its links are in the test                 |    |

|      | mode and others are in the operational mode                                                   | 53 |

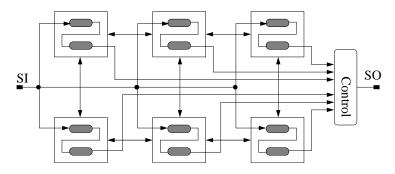

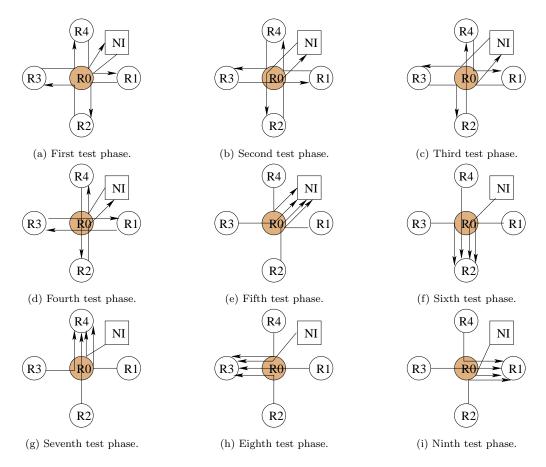

| 2.27 | Different test phases for a router having four neighbors and one dedicated                    |    |

|      | network interface (NI). First four phases cover data path and all routings                    |    |

|      | without any arbitration while rest of the phases cover control logic in arbiter               |    |

|      | and FIFOs                                                                                     | 53 |

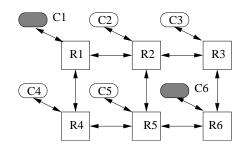

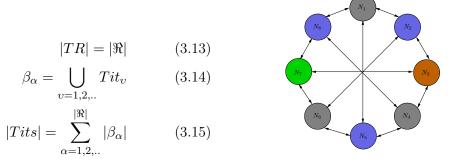

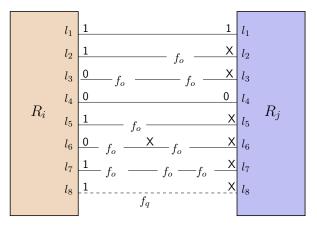

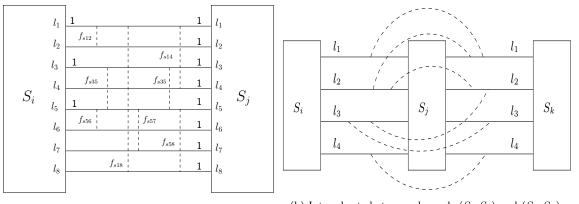

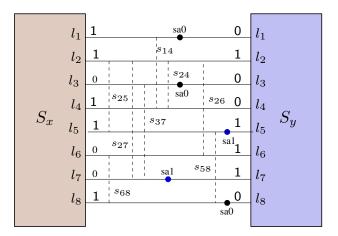

| 3.1  | Single/multiple existences of stuck-at faults in the channel $(S_i, S_j)$                     | 69 |

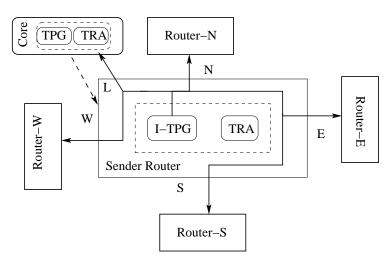

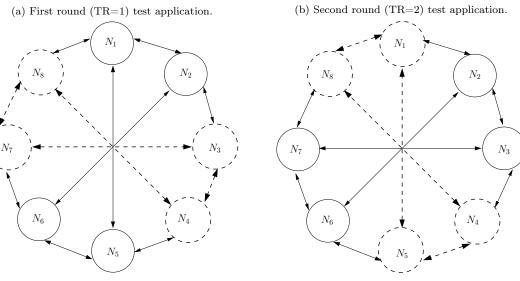

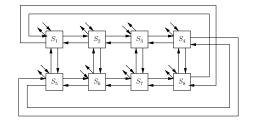

| 3.2  | A general view of test module for addressing SAFs in channels. $\ldots$ .                     | 71 |

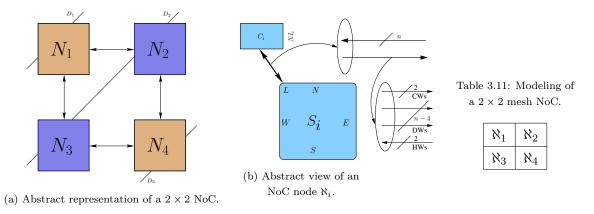

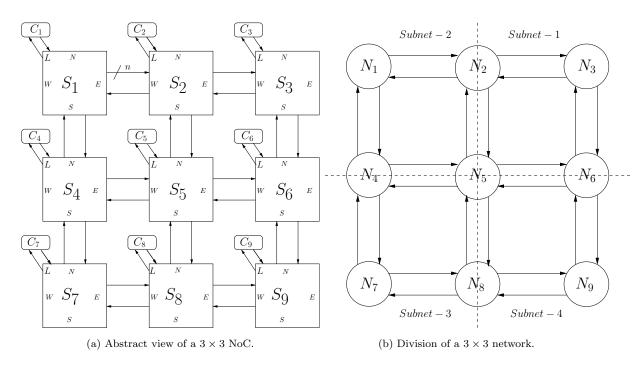

| 3.3  | High level view of a $2 \times 2$ NoC architecture and its node                               | 78 |

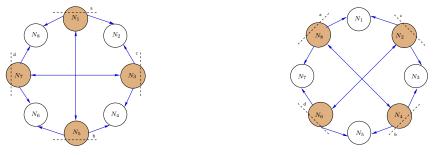

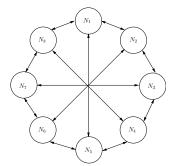

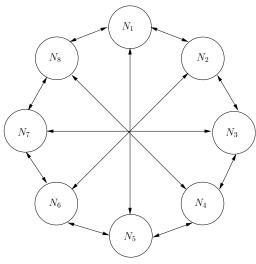

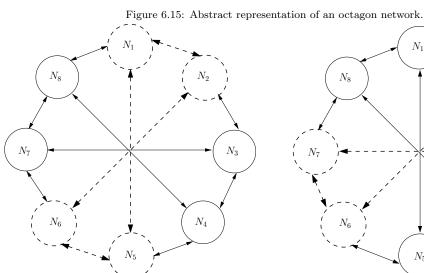

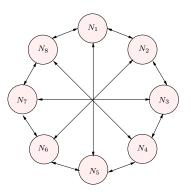

| 3.4  | Abstract representation of an octagon NoC                                                     | 78 |

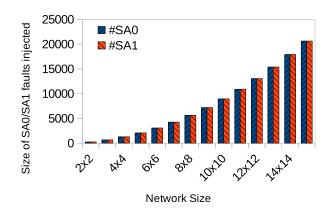

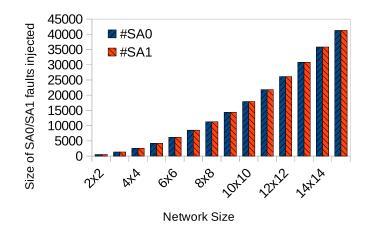

| 3.5  | Fault injection campaign in 16-bit NoCs                                                       | 81 |

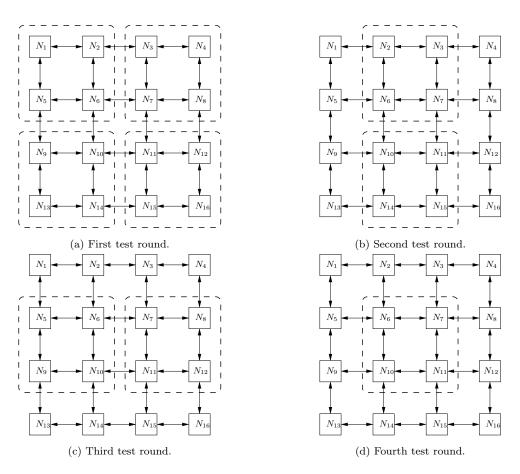

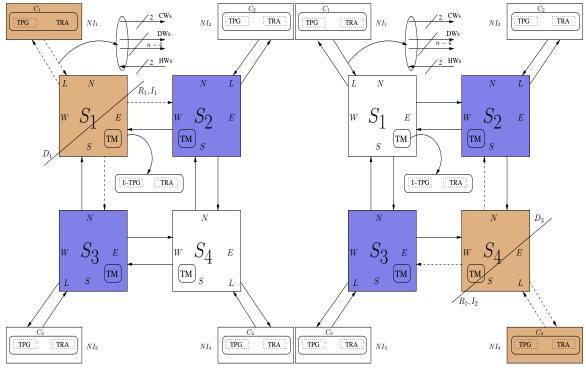

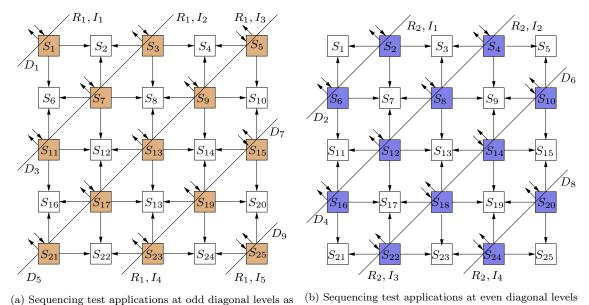

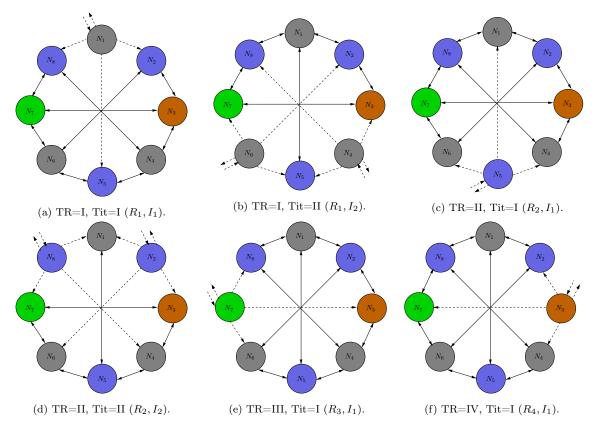

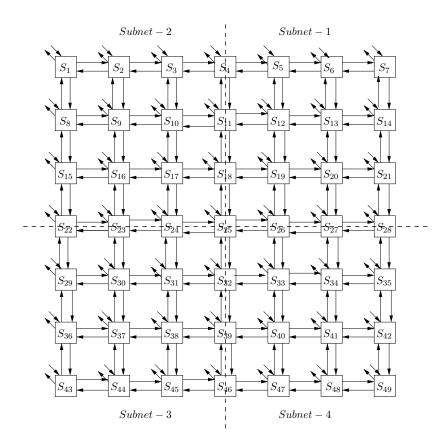

| 3.6  | Application of the proposed test solution at different test rounds and iterations             |    |

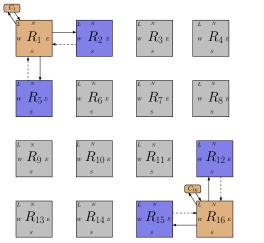

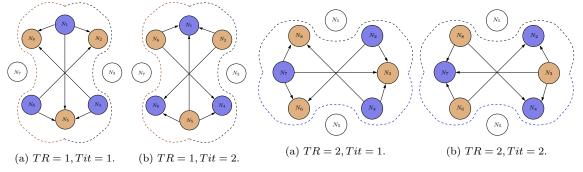

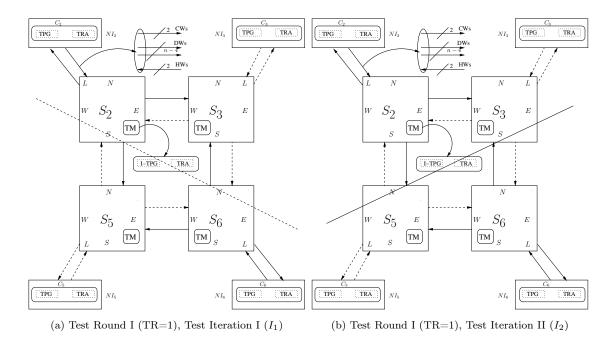

|      | on a $2 \times 2$ mesh NoC with <i>n</i> -bit unidirectional channel configuration            | 82 |

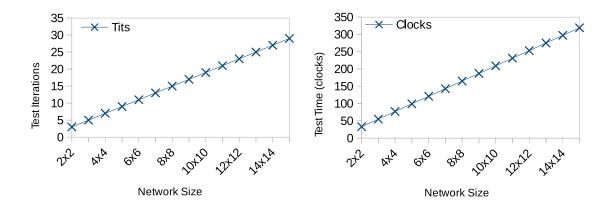

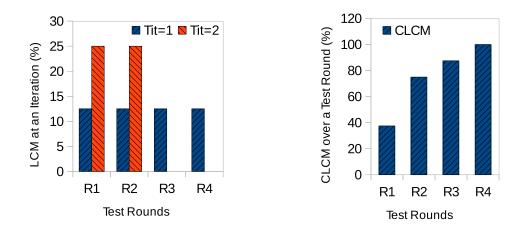

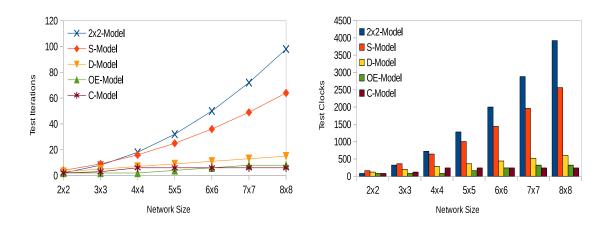

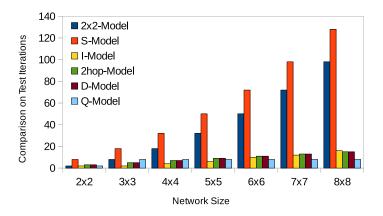

| 3.7  | Number of test iterations vs. NoC Size.                                                       | 83 |

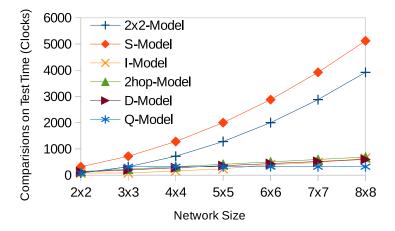

| 3.8  | Amount of test time vs. NoC Size.                                                             | 83 |

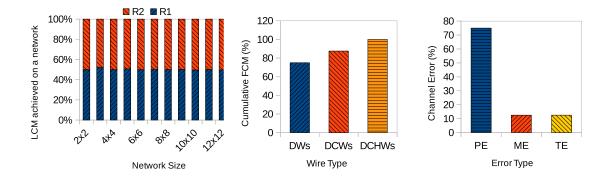

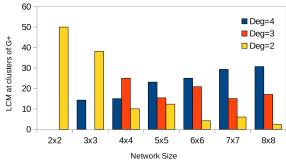

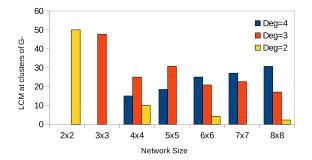

| 3.9  | Cumulative LCM vs. NoC Size                                                                   | 85 |

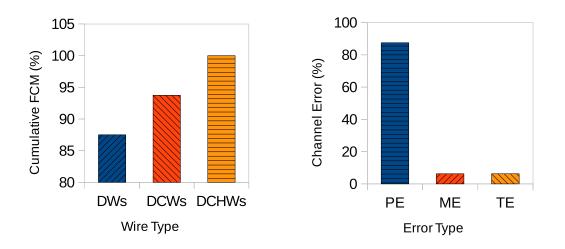

| 3.10 | Cumulative FCM in networks with 16-bit channels                                               | 85 |

| 3.11 | Expected channel error in networks with 16-bit channels                                       | 85 |

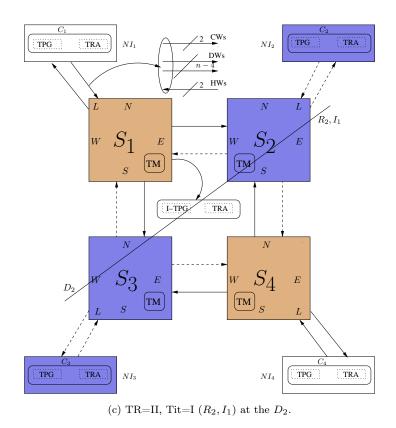

| 3.12 | On-line evaluation of the proposed test solution applied at both test rounds on               |    |

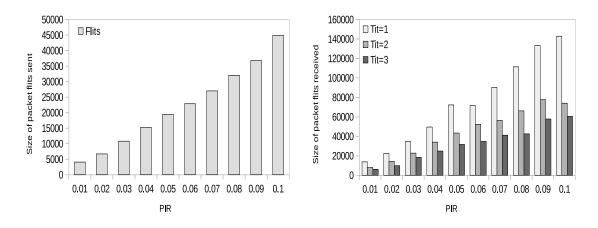

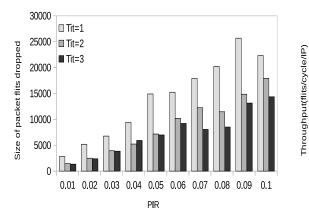

|      | the 16-bit $2 \times 2$ NoC                                                                   | 87 |

| 3.13 | Application of the proposed test solution at different test rounds and iterations             |    |

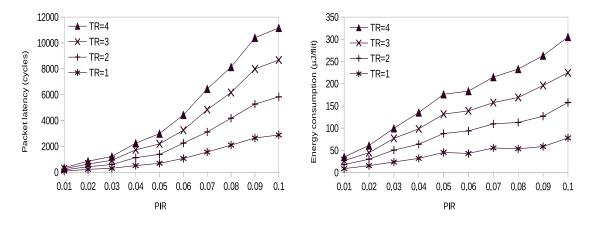

|      | on $15 \times 15$ NoC with unidirectional channel configuration.                              | 89 |

| 3.14 | On-line evaluation of the proposed test solution applied at both test rounds on               |    |

|      | the 16-bit $15 \times 15$ NoC.                                                                | 90 |

| 3.15 | Fault injection campaign in 32-bit NoCs                                                       | 91 |

| 3.16 | Cumulative FCM in networks with 32-bit channels                                               | 92 |

| 3.17 | Expected channel error in networks with 32-bit channels                                       | 92 |

| 3.18 | Application of the proposed test solution at different test rounds and iterations             |    |

|      | on 5 $\times$ 5 NoC with unidirectional channel configuration                                 | 94 |

| 3.19 | On-line evaluation of the proposed test solution applied at both test rounds on               |    |

|      | the $5 \times 5$ NoC with 32-bit channels.                                                    | 95 |

| 3.20 | Application of the proposed test solution at different test rounds and iterations                                     |     |

|------|-----------------------------------------------------------------------------------------------------------------------|-----|

|      | on an octagon NoC with unidirectional channel configuration.                                                          | 96  |

| 3.21 | LCM achieved on a test round in octagon network with 16-bit channels                                                  | 97  |

| 3.22 | Cumulative LCM achieved on a test round in octagon network                                                            | 97  |

| 3.23 | On-line evaluation of the proposed test solution applied at the test rounds on                                        |     |

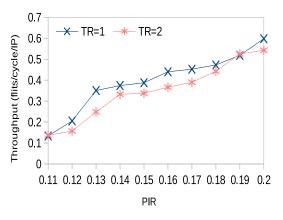

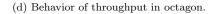

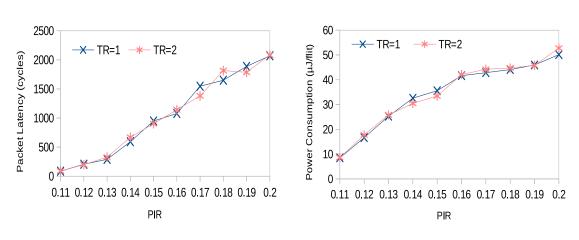

|      | the octagon NoC with 16-bit channels.                                                                                 | 98  |

| 3.24 | Comparison on payload error vs. Test models on networks of 16-bit channels.                                           | 103 |

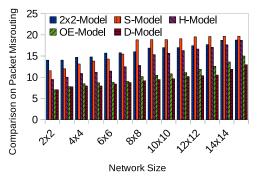

| 3.25 | Comparison on misrouting error vs. Test models on networks of 16-bit channels.                                        | 103 |

| 3.26 | Comparison on timeout error vs. Test models on networks of 16-bit channels.                                           | 103 |

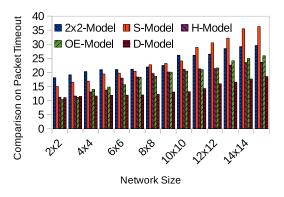

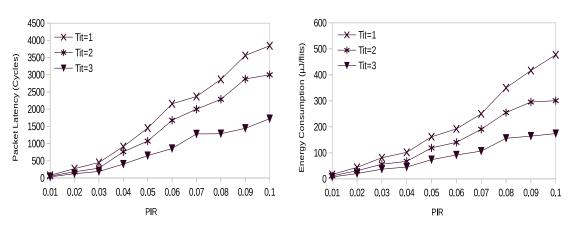

| 3.27 | Improvement (%) on packet latency by the proposed D-Model over existing                                               |     |

|      | test models                                                                                                           | 104 |

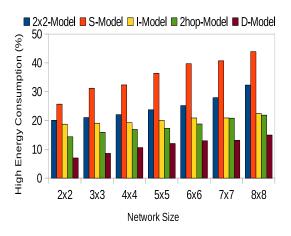

| 3.28 | Improvement (%) on energy consumption by the proposed D-Model over                                                    |     |

|      | existing test models.                                                                                                 | 104 |

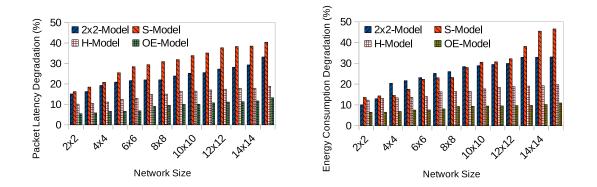

| 4.1  | Abstract representation of an NoC node and a channel. $R_i, C_i$ are a router and                                     |     |

|      | its core, respectively. $N_i \leftarrow \langle R_i, C_i \rangle$ is node. $NI_i$ is a wrapper that wraps the $C_i$ . | 108 |

| 4.2  | Representation of open faults in the channel $(R_i, R_j)$                                                             | 113 |

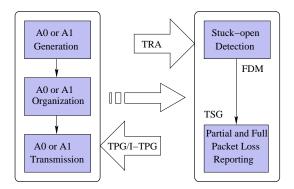

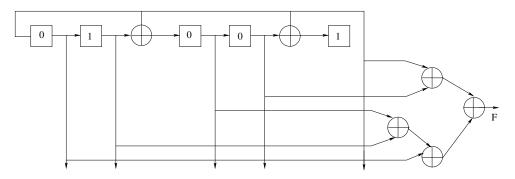

| 4.3  | A general view of test module for addressing open faults in channels                                                  | 116 |

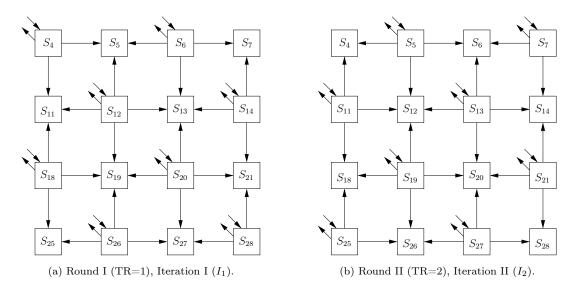

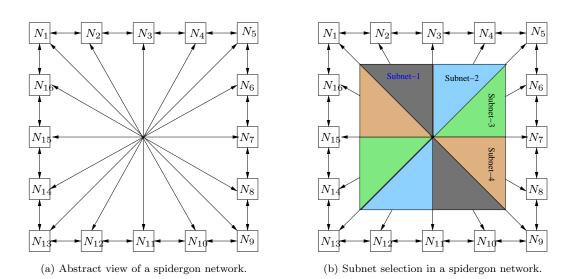

| 4.4  | Graphical representation of various NoC architectures.                                                                | 122 |

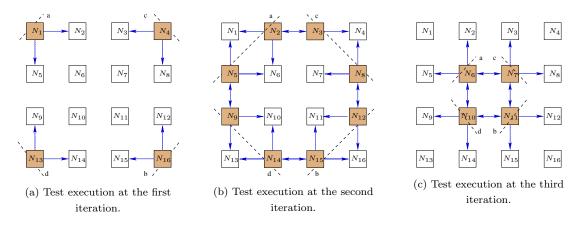

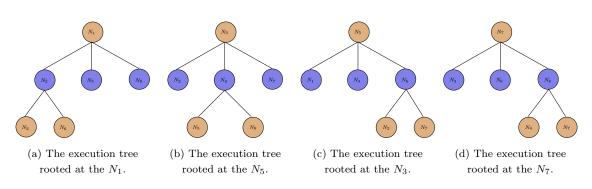

| 4.5  | Execution of the test mechanism driven by the 4-corner principle in a $4\times 4$                                     |     |

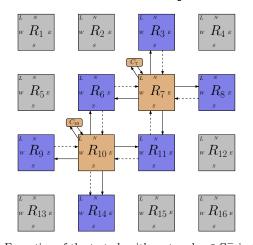

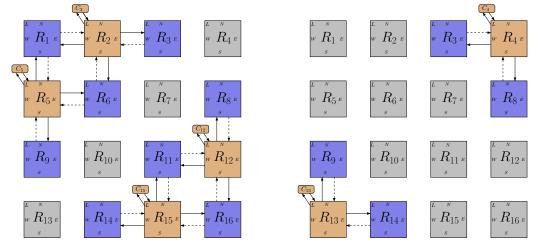

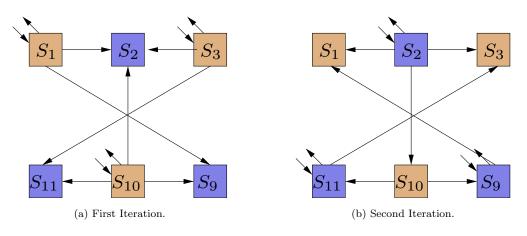

|      | network.                                                                                                              | 125 |

| 4.6  | The 4-corner forest on execution of the test mechanism initiated from corner                                          |     |

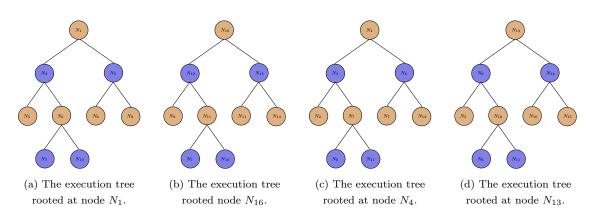

|      | nodes of the $4 \times 4$ network                                                                                     | 125 |

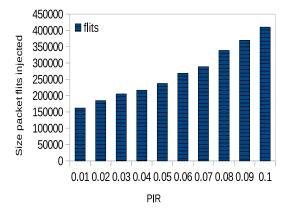

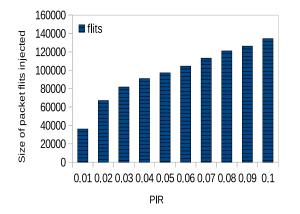

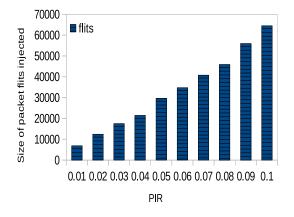

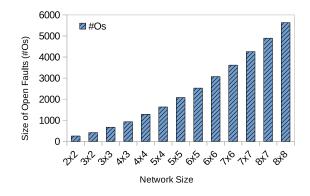

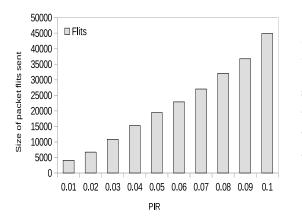

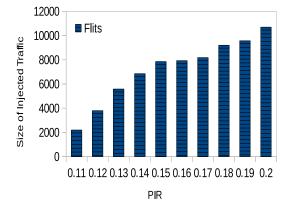

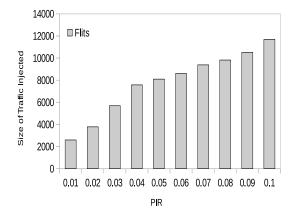

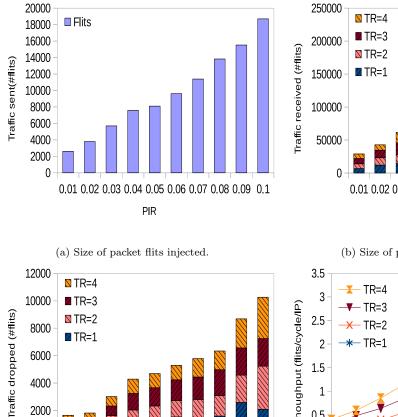

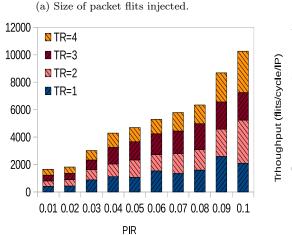

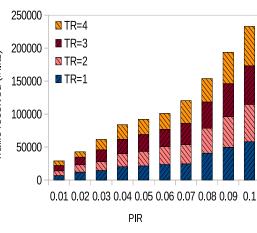

| 4.7  | The size of open faults injected in the 16-bit networks                                                               | 129 |

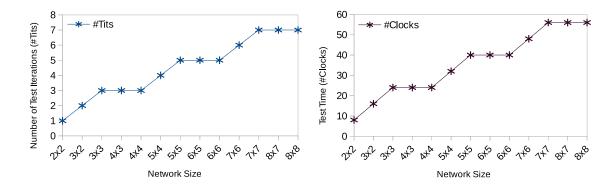

| 4.8  | The number of test iterations required to detect open faults in the $P \times Q$ networks.                            | 132 |

| 4.9  | The test time incurred by the 4-corner driven test mechanism in the 16-bit                                            |     |

|      | $P \times Q$ networks                                                                                                 | 132 |

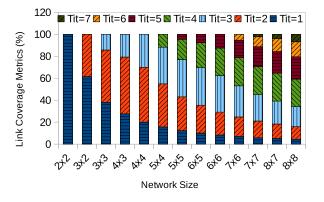

| 4.10 | The LCM achieved on test executions in the 16-bit $P \times Q$ networks                                               | 132 |

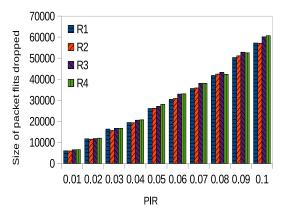

| 4.11 | Size of open faults detected in a test iteration on a 16-bit $P\times Q$ network.<br>                                 | 132 |

| 4.12 | On-line evaluation of the proposed test solution applied at the corner nodes                                          |     |

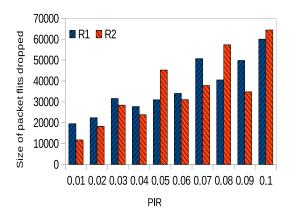

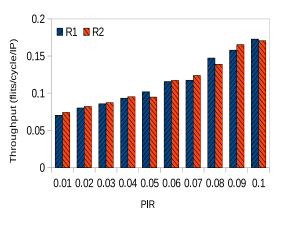

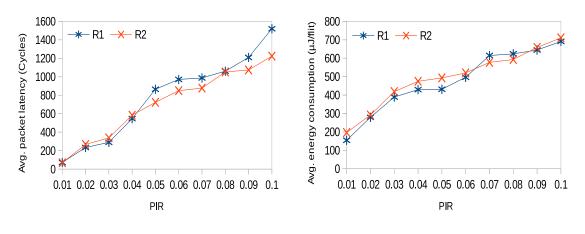

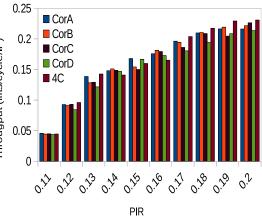

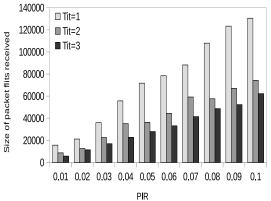

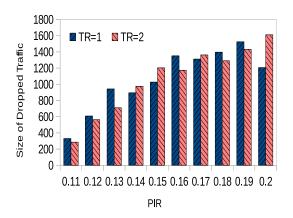

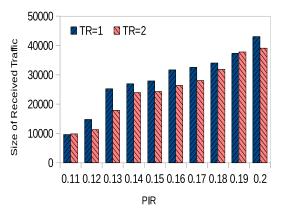

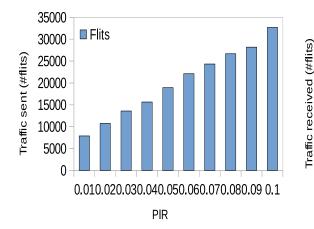

|      | separately and concurrently on the 16-bit $4 \times 4$ mesh NoC                                                       | 135 |

| 4.13 | The size of open faults injected in the 32-bit networks                                                               | 137 |

| 4.14 | Size of open faults detected in a test iteration on the 32-bit NoCs                                                   | 138 |

| 4.15 | On-line evaluation of the proposed test solution applied at the corner nodes                                          |     |

|      | separately and concurrently on the the 32-bit $4 \times 4$ mesh NoC                                                   | 139 |

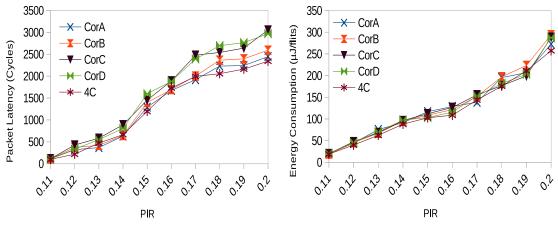

| 4.16 | Test executions from the corner nodes on the $8 \times 8$ network                                                     | 141 |

| 4.17 | The 4-corner forest on the test application initiated from the corner nodes on                                        |     |

|      | the $8 \times 8$ network.                                                                                             | 141 |

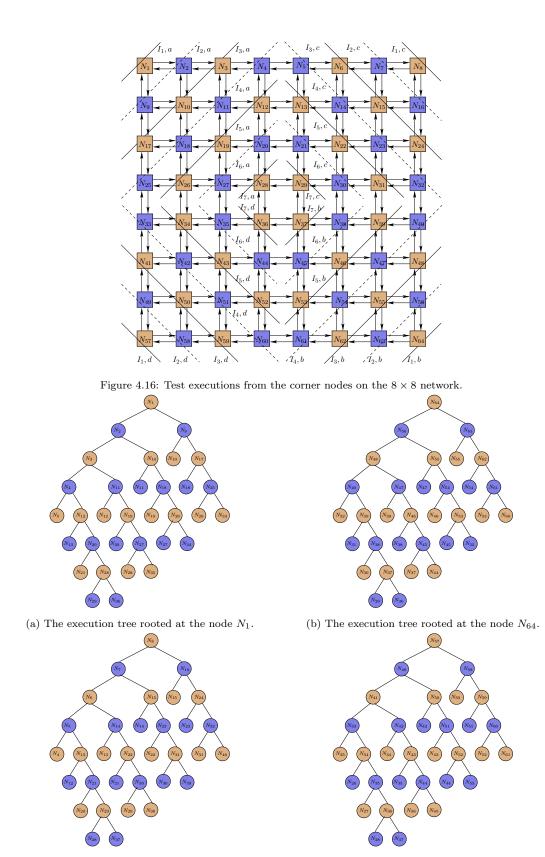

| 4.18                                                                                         | On-line evaluation of the proposed test solution applied at the corner nodes                                                                                                                            |                                                                                          |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|                                                                                              | separately and concurrently on the 16-bit $8 \times 8$ mesh NoC                                                                                                                                         | 142                                                                                      |

| 4.19                                                                                         | The execution of the test mechanism driven by the 4-corner principle on the                                                                                                                             |                                                                                          |

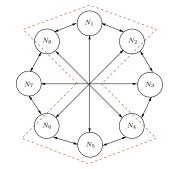

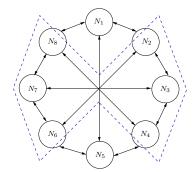

|                                                                                              | the octagon network.                                                                                                                                                                                    | 144                                                                                      |

| 4.20                                                                                         | The 4-corner forest on execution of the test mechanism initiated from corner                                                                                                                            |                                                                                          |

|                                                                                              | nodes of an octagon NoC.                                                                                                                                                                                | 144                                                                                      |

| 4.21                                                                                         | Representation of an octagon network into an equivalent $2 \times 4$ network                                                                                                                            | 145                                                                                      |

| 4.22                                                                                         | On-line evaluation of the proposed test solution applied at the corner nodes                                                                                                                            |                                                                                          |

|                                                                                              | separately and concurrently on the 16-bit octagon NoC                                                                                                                                                   | 146                                                                                      |

| 4.23                                                                                         | Comparisons on hardware area overhead among the test models                                                                                                                                             | 147                                                                                      |

| 4.24                                                                                         | Improvement on hardware area overhead by the 4C-Model over prior works                                                                                                                                  | 147                                                                                      |