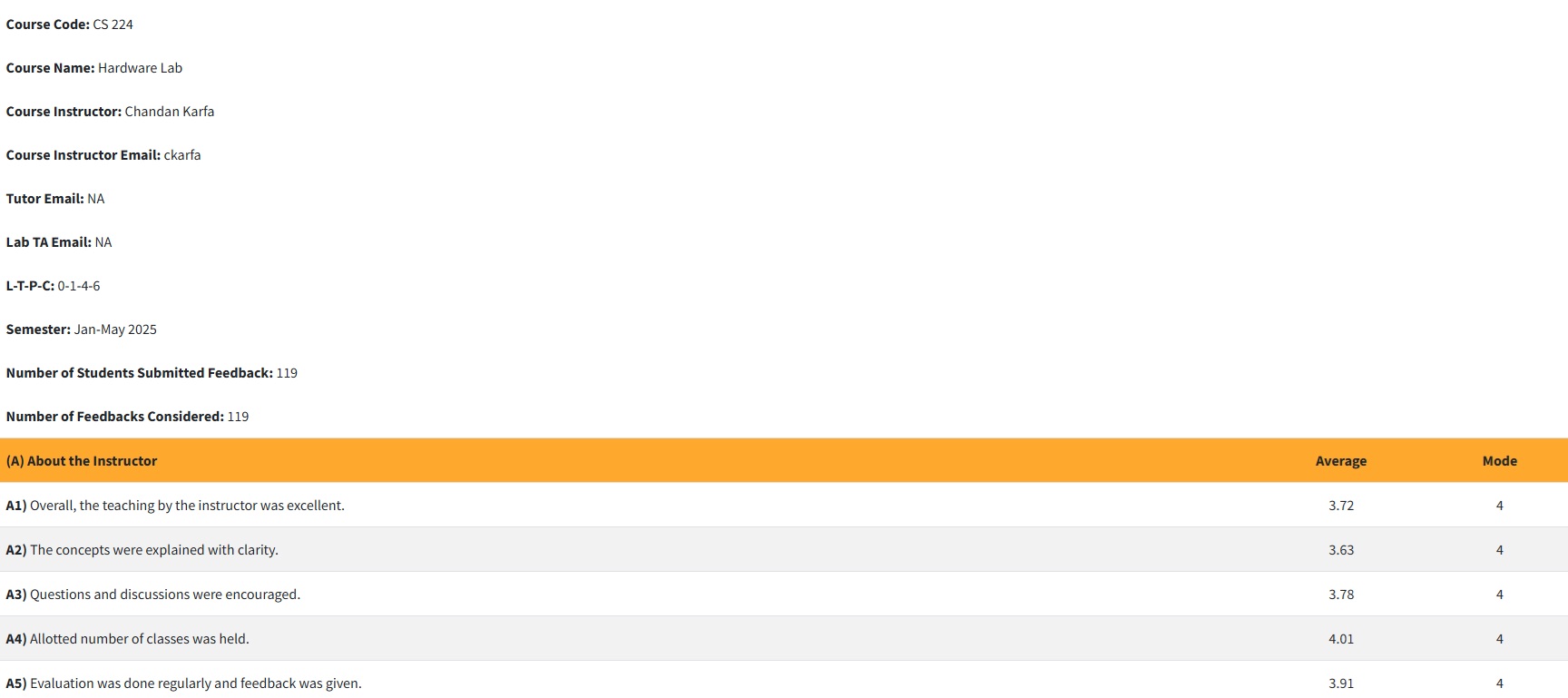

Chandan Karfa

CS224: Hardware Lab

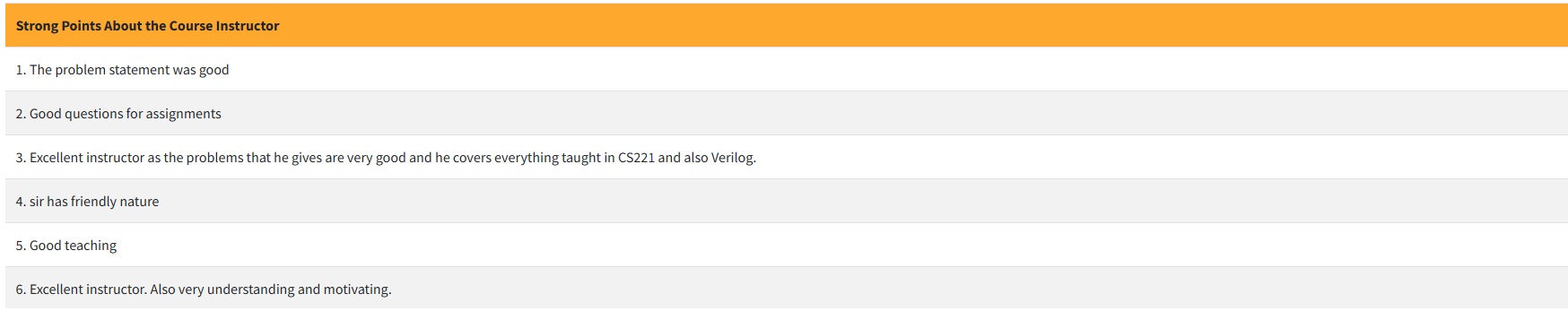

Course Feedback:

|

|

Announcements:

Welcome to Hardware Lab

ICs available in our HW Lab PDF

Tutorial and Lab Timing and Venue:

Tuesday: 2PM-5PM

Venue: Hardware Lab

Tutorial Timing and Venue:

Tuesday: 5PM-5:55PM.

Venue: 5G4

Instructor

Dr. Chandan Karfa

Dr. Sukanta Bhattacharjee

TAs:

| Name | Email Id |

| Nilotpola Sarma | |

| Praveen Karmakar | |

Grade Calculation

Each Assignment will have different weightage based on difficultiy level.

Assignment 1: 7%

Lab Schedule

| Sl No | Assignments | Weightage | Evaluation Date |

| 1 | 4 bit ALU using Breadboard | 5% | 23rd January 2024 |

| 2 | Design Gray code to Binary code conversion circuit in Breadboard | 8% | 28th January 2025 |

| 3 | 4 bits two inputs Carry Look Ahead Adder (CLA) and Carry Save Adder in FPGA and Breadboard (only 3 bit CLA) | 10% | 11th February 2025 |

| 4 | Implement a 4-bit Synchronous Binary UP or UPDown counter in Breadboard | 7% | 18th February 2025 |

| 5 | RTL Implement a C function in Verilog and demonstrate using FPGA | 10% | 18th March 2025 |

| 6 | Implement in Gate level MaxMin Finding Algorithm in Verilog and demonstrate in FPGA | 10% | 1st April 2025 |

| 7 | Efficient Implementations of long chain addition in Verilog and demonstration using FPGA | 10% | 10th April 2025 |

| 8 | Implement a subset of the MIPS processor | 10% | 22nd April 2025 |

Tutorial Schedule

| Sl No | Date | Assignments | Topics |

| 1 | 16th January 2024 | Introduction to CS224 | |