CS221:Digital Design

Instructor: Dr. A. Sahu

Semester Marks

Course Structure | Lecture Slides | Assignments | Books | ClassTiming, Venue and Rules

- Boolean Algebra and switching functions; Minimization and realization using logic gates, ROMs, PLAs, multiplexers;

- Circuits for code conversion; Flip-flops, registers, counters;

- Finite state model: State tables and diagrams; State minimization; Excitation functions of memory elements;

- Synthesis of synchronous sequential circuits; Representation and synthesis using ASM charts; Incompletely specified machines;

Mid Semester

- Specification and synthesis of asynchronous sequential machines;

- Number representation: fixed and floating point; Addition, subtraction, multiplication and division of numbers.

- Current trends in digital design: ASIC, FPGA, etc.;

Thanks to Prof. Anshul Kumar (CSE, IIT Delhi), Frank Vahid (Book Author Digital Design) for providing PDF/PPT Slides

- 26 JUL 2011: Introduction to Digital Design PDF Slides

- 27 JUL 2011: Number System PDF Slides

- 01 AUG 2011: Operations in Number System and Boolean Algebra PDF Slides

- 02 AUG 2011: Boolean Algebra and TheoremsPDF Slides

- 03 AUG 2011: Gates, Truth Table, Min Term, MaxTerm, Canonical Form PDF Slides [[[Mano Book and Vahid Book]]]

- 08 AUG 2011: KMap-Logic Minimization PDF Slides

- 09 AUG 2011: KMap-Logic Minimization PDFSlides

- 10 AUG 2011: KMap-Logic Minimization PDFSlides

16 AUG 2011: Logic Minimization and complexity of Algorithms No Slides

17 AUG 2011: Quiz (BCD to 7 Segment Decoder) No Slides

- 19 AUG 2011: MUX and Decoder, Logic Implementation using MUX/Decoder PDF Slides

- 22 AUG 2011: Adders/BCD Adder Delays, Quine-McCluskey (QM) Logic Minimization Motivation and Examples PDF Slides

- 23 AUG 2011: QM Examples and Programming Method, Complexity PDF Slides[[[Mano Book]]]

Assignment 1: Statement of Assignments 1

- 24 AUG 2011: Sequential Logic Design: SR Latch PDF Slides

- 29 AUG 2011: SR Latch (Race Condition: Ensure, Stabilize, Store), D latch, Clocked Flip Flop PDF Slides

- 30 AUG 2011: FlipFlop: Level/Edge Sensitive, Master Slave, J-K and FF Universality, Characteristic Equations PDF Slides [[[ Givone Book]]]

- 05 SEP 2011: Register (Storing State Example), Introduction to FSM PDF Slides

- 06 SEP 2011: FSM and Examples PDF Slides

- 07 SEP 2011: FSM Controller Implementation PDF Slides [[[ Vahid Book]]]

- 12 SEP 2011: FSM Controller Examples: Press button Sync, Sequence Generator, 2 bit Binary Counter, FSM Controller using Other FFs PDF Slides

- 13 SEP 2011: Counters, Top Down Approaches to Digital System, Frequency Divider, Timer, Digital ClockNo Slides

- 14 SEP 2011: Counters (Binary(Sync/Async), Mod N Counter, FF Excitation Table, Counter using D/T/JK/RS FFs) PDF Slides [[[ Givone Book]]]

20 SEP 2011 : Mid Semester Exam 10AM-12Nn: Exam Venue (Room 2201/2202/2203/2204) Question Uploaded on 8th Oct

- 26 SEP 2011: Mid Semester Question and Model Answer Discussion PDF Slides

- 27 SEP 2011: Counter Based on Shift Register PDF Slides

- 28 SEP 2011: Designing of Multi Function Register PDF Slides [[[ Vahid Book ]]]

- 11 OCT 2011: Adder (Basic Model: Ripple carry Model), Carry Analysis (Generation, Propagation, Kill) PDF Slides [[[ Ercegovac and Lang Book ]]]

[[[Supplementary Material:http://www.cs.ucla.edu/digital_arithmetic/files/ch2.pdf ]]]

- 12 OCT 2011: Adder Manchester, Carry Skip and Carry Select PDF Slides

- 14 OCT 2011: Adder Delay Analysis: RCA, mRCA, CSkipA, CSelA and Logarithmic Adder (Carry look ahead Adder) PDF Slides [[[ Ercegovac and Lang Book ]]]

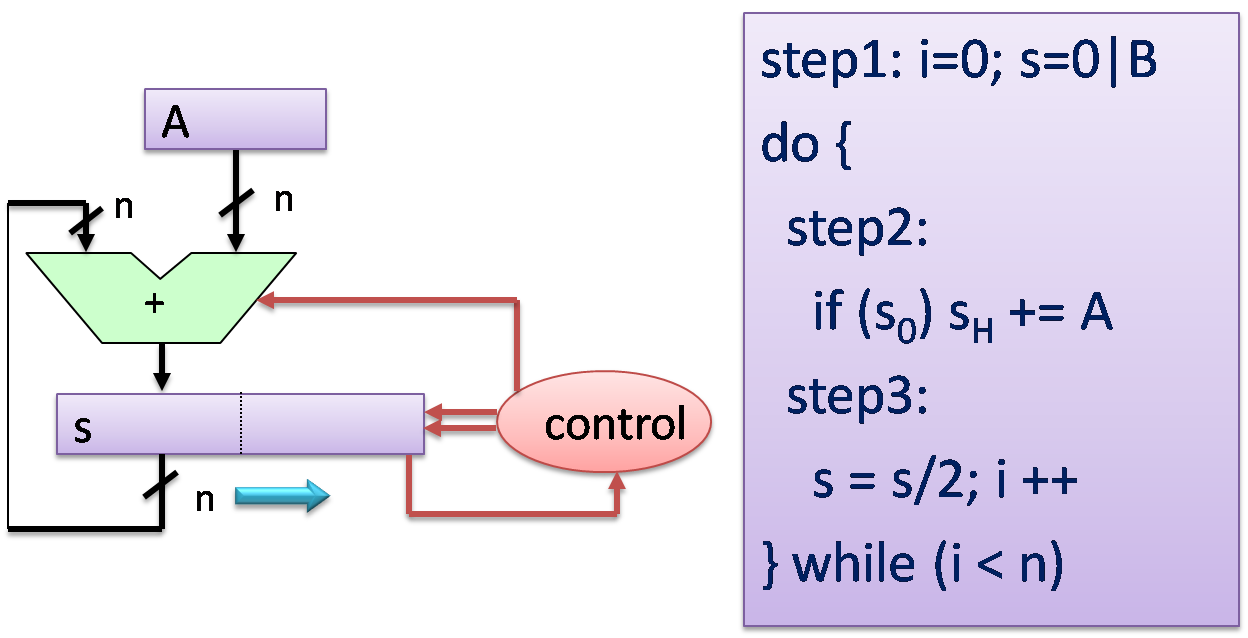

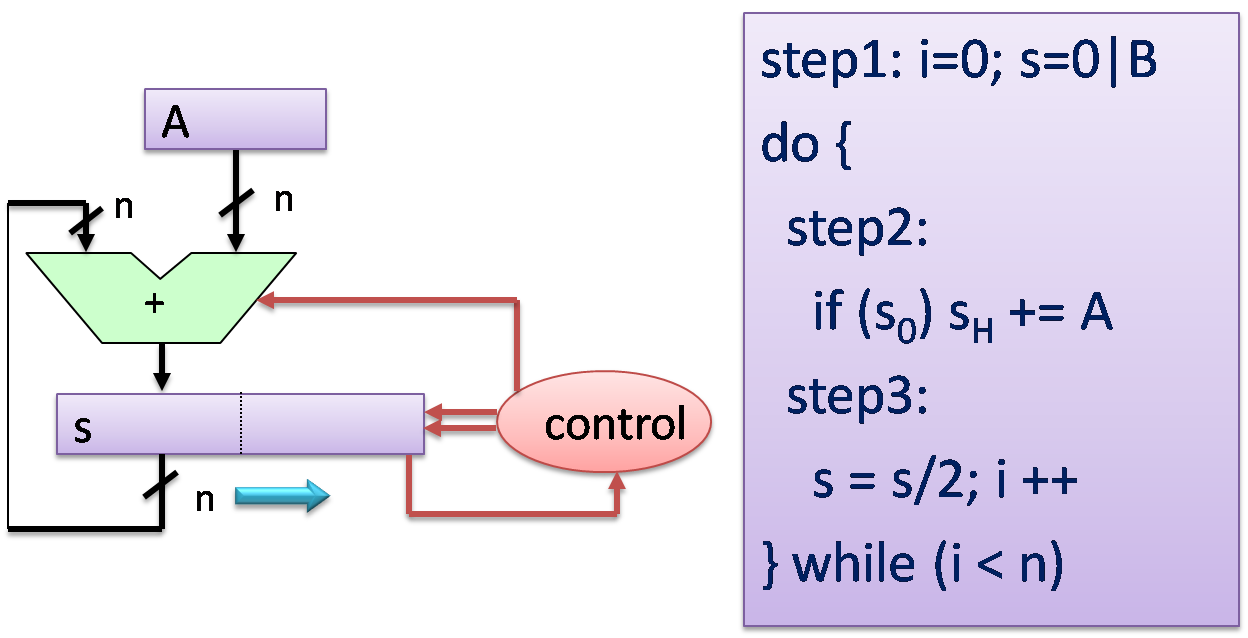

- 17 OCT 2011: Multiplication and quiz PDF Slides

- 18 OCT 2011: Multiplication PDF Slides

- 19 OCT 2011: Division PDF Slides

- 24 OCT 2011: Floating points: Representation (float,double), Density, Operation and Accuracy (X+1=X) PDF Slides

- 25 OCT 2011: HDL IntroductionPDF Slides

- 28 OCT 2011: VHDL: Syntax, Model, Test Bench and Tool (GHDL and GTKWAVE) PDF Slides

- 31 OCT 2011: VHDL: Test Bench, Package, Library, Generic/generate, (Adder, Mux, Register) PDF Slides

- 01 Nov 2011: VHDL: Model and Synthesis PDF Slides

- 02 Nov 2011: Introduction to High level Synthesis [[No Slides]]

- 07 Nov 2011: Introduction to VLSI Design for ASIC(Clock, Power, Placement, Routing) [[No Slides]]

- 08 Nov 2011: Introduction to FPGA Design [[No Slides]]

- 14 Nov 2011: Introduction to Embedded System [[No Slides]]

- 15 Nov 2011: Feedback, Summery of CS221, Future Courses,End Semester Exam Pattern [[No Slides]]

Assignment 3: Implement an 32 bit unsigned integer multiplier using VHDL programming language and GHDL tools: (10 marks) Announced On 31-Oct-2011, Deadline:12-Nov-2011

- Statement:

Implement an 32 bit unsigned integer multiplier using VHDL.

(a) Implement both Data Path (One 32 bit Adder, One Shift Register (S), One Register (A)) and Controller (Please look at Lecture 27, Sequential add and shift multiplier 3)

(b) Implement a test bench which supply stimulus to multiplier

(c) Controller can be designed using FSM and was discussed in Quiz 2

Inputs are unsigned integers and also output is a unsigned integer of may be 64 bit.

You have to simulate and show the GTKwave output of designed multiplier

Use GHDL: A tutorial of GHDL is available here : http://ghdl.free.fr/ghdl/index.html

GHDL example are from : VHDL Example Taken from http://esd.cs.ucr.edu/labs/tutorial/

Download and Install GHDL and GTKWAVE : GHDL and GTKWAVE

(a) Untar GHDL.tgz, Read INSTALL File and follow the instruction to install ghdl

(b) Untar GTKWAVE sources; and issue these command $./configure --prefix=$pwd --disable-tcl ; make ; make install

- Write a small document 2/3 pages (Readme, how to compile/run/how it work) and submit

- Deadline: 12-Nov-2011, 11.55 PM (before Mid night) Copy Case Lead to F Grade. After deadline grading: 1 mark deduction per day

- Submission procedureSend compressed (tar/gz/tgz/zip) version of directory containing all codes(vhd, vcd, makefile,..) and readme Document) to asahu AT iitg DOT ernet.in with “CS221 Assignment 3” as subject

Assignment 2: Writing C/C++ program to report optimal group size for carry

skip addition (10 marks) Announced On 16-Oct-2011, Deadline:26-Oct-2011

- Statement:

Write a C/C++ program to report optimal group size for 10,000 carry

skip addition, where input two 32 bit numbers are randomly generated

for each carry skip addition.

- group size can be vary from 3 to 8

- If group size is 6, groups are (31,30,29,28,27,26),

(25,24,23,22,21,20), (19,18,17,16,15,14), (13,12,11,10,9,8),

(7,6,5,4,3,2) and (1,0).

- Last group contain less number of bits, 32%6=2bits.

Optimal group size means: Finding maximum value of (Number of Skip * Group size).

- You are allowed to use in build functions and data structure of C++ STL. C++ STL have inbuild function for

stack, vector, list, sorting..

- Write a small document 2/3 pages (Readme, how to compile/run/how it work) and submit

- Deadline: 26-Oct-2011, 11.55 PM (before Mid night) Copy Case Lead to F Grade. After deadline grading: 1 mark deduction per day

- Submission procedureSend compressed (tar/gz/tgz/zip) version of directory containing all codes(C/C++) and readme Document) to asahu AT iitg DOT ernet.in with “CS221 Assignment 2” as subject

Assignment 1: Implementation of Quine-McCluskey Logic Minimization (10 marks) Announced On 25-Aug-2011, Deadline:10-Sep-2011

- Statement:

Implementation of Quine-McCluskey Logic Minimization: Your program should be able solve more than 10 variable logic minimization. Inputs to your program are to be generated automatically by randomization method.

Basically three inputs: number of variable, number of min-terms and a vector of min-terms Example: 8, 12, [0, 10, 22, 56, 83, 88, 104, 138, 144, 201, 209, 240, 255]. The number of variable can be fixed either 8, 9 or 10. But the number of min-terms and vector of min-terms are to be generated automatically.

// Pseudo code to generate randomly min-terms

srand(your_roll_number); // Inputs depend upon your roll-number

number_of_minterm=rand()% pow (2,num_variable);

for(i=0;i to number_of_minterm;i++){

Minterms[i]=rand()%pow (2,num_variable);

}

- You are allowed to use in build functions and data structure of C++ STL. C++ STL have in build function for

stack, vector, list, sorting..

- Write a small document 2/3 pages (Readme, how to compile/run/how it work) and submit

- Deadline: 10-Sep-2011, 11.55 PM (before Mid night) Copy Case Lead to F Grade. After deadline grading: 1 mark deduction per day

- Submission procedureSend compressed (tar/gz/tgz/zip) version of directory containing all codes(C/C++) and readme Document) to asahu AT iitg DOT ernet.in with “CS221 Assignment 1” as subject

Text:

- Frank Vahid, Digital Design (Preview Edition), Wiely India Edition, 2005

- M. Morris Mano and M. D. Ciletti, Digital Design, 4/e, Pearson Education, 2007.

- Donald D. Givone, Digital Principles and Design, McGraw-Hill, 2003

References:

- Ercegovac and Lang, Digital Arithmetic, Morgan Kauffman, 2004

- R. H. Katz and G. Boriello, Contemporary Logic Design, 2/e, Prentice Hall of India, 2009.

- Venue: 1201

- Timing: Mon 9AM-10AM, Tue 10AM-11AM, and Wed 11AM-12Noon

- Rules :

- 75% attendance mandatory

- Attendee will be calculated before end semester examination

- 3 Assignment, 2 Quiz and 1 Take home

- 25% Assignment + 35% mid semester + 40% end semester