Chandan Karfa

CS 221: Digital Design

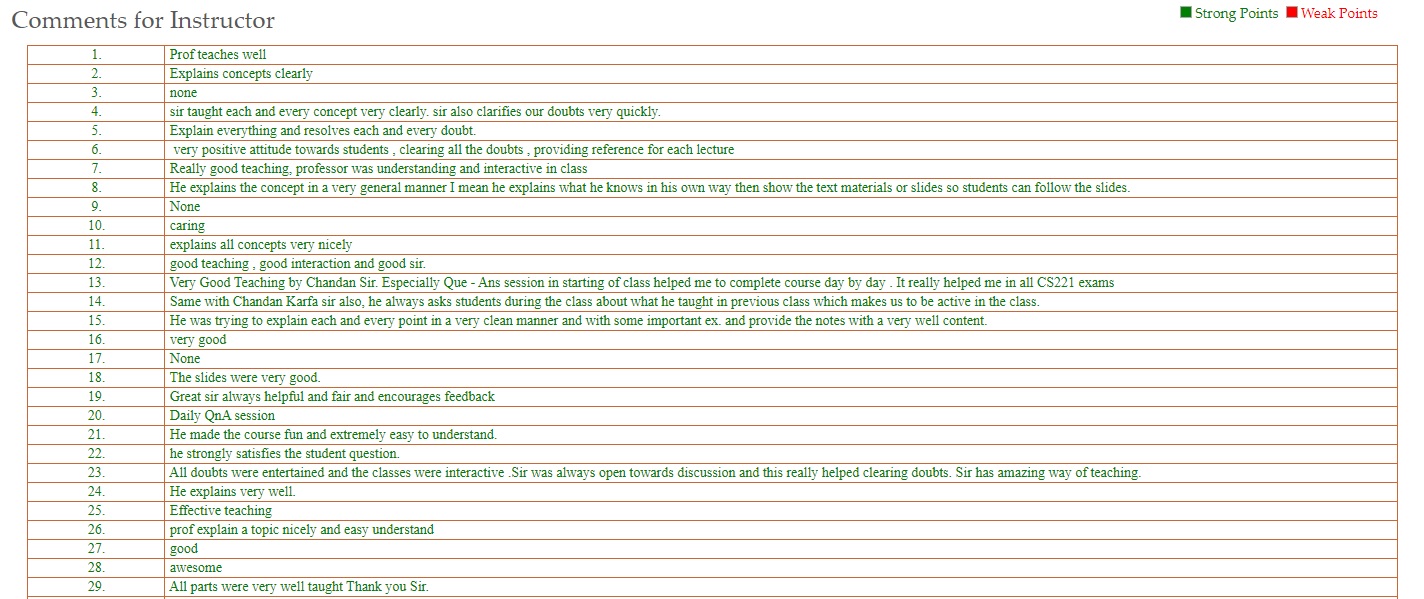

Feebback on Course Instructor:

|

|

Welcome to CS 221 Course page

16th August 2021: Quiz 1 is scheduled on 25th August 2021, 6PM-6:30PM, over MS teams using MS forms.

24th July 2021: The course will be taught online using MS Teams Platform. You will be added to the course page in MS teams.

24th July 2021: There will be live lectures in the scheduled time. Attending online class is mandetory. The video recording of the class will be posted on youtube for future reference.

IMPORTANT: Any malpractice will lead to F grade without any explanation.

Instructors

Dr. Chandan Karfa (till Mid-Semester)

Dr. Aryabartta Sahu (post Mid-Semester)

Class Timing and Venue:

Monday: 10AM-11AM, Thursday: 9AM-10AM, Friday: 9AM-10AM.

Venue: MS Teams

TAs with their Responsibilities:

Debabrata Senapati - debab176101003@iitg.ac.in

Priyanka Panigrahi - priya176101006@iitg.ac.in

K Chitra - k.chitra@iitg.ac.in

Nilotpola Sarma - s.nilotpola@iitg.ac.in

Surajit Das - d.surajit@iitg.ac.in

Subham Das - subham.das@iitg.ac.in

Abhik Paul - apaul@iitg.ac.in

Mukul Chaturvedi - mchaturvedi@iitg.ac.in

Syllabus:

Review of Boolean algebra and logic minimisation;

Design of combinational logic blocks (MUX, DeMUX, encoder, decoder, adders, multipliers, etc.);

Design using combinational logic blocks;

Sequential circuit design: flip-flops, FSM, registers, counters, state tables and diagrams, state minimization, excitation functions of memory elements, synthesis of synchronous sequential circuits; representation and synthesis using ASM charts;

Specification and synthesis of asynchronous sequential machines;

Basics of FPGA architecture;

Progamming using HDLs (Verilog).

Text Book:

[Mano] M. M. Mano and M. D. Ciletti, Digital Design, 5th Ed., Pearson Education.

[Kohavi] Z. Kohavi and N. Jha, Switching and Finite Automata Theory, 3rd Ed., Cambridge University Press, 2010.

References:

[Palnitkar] S. Palnitkar, Verilog HDL: A Guide to Digital Design and Synthesis,Pearson, 2nd Ed, 2003.

[Vahid] F. Vahid, Digital Design, 1st Ed., Wiley India, 2011.

Grade Calculation

Quiz: 40%. 4 Quizzes, two before mid-sem and two after mid-sem. Each carries 10% marks.

Mid-Sem Examinations: 20%.

End-Sem Examinations: 30%

Class Participation: 10%. It includes attendance, class interaction and class performance.

Classes

| Lecture No | Date | Topic | Resources |

| 1 | 28th July 2021 | Introduction to Digital Logic | |

| 2. | 29th July 2021 | Switching_Algebra | Kohavi: Ch3 |

| 3. | 2nd August 2021 | Number Systems | Kohavi: Ch 1 |

| 4. | 5th August 2021 | Binary Codes | Kohavi: Ch 1 |

| 5. | 6th August 2021 | Error Detection Correction Codes | Kohavi: Ch 1 |

| 6. | 9th August 2021 | Minimization of Switching functions: Karnaugh Map, prime implicants | Kohavi: Ch 4 |

| 7. | 12th August 2021 | Tabulation method for determination of prime implicants | Kohavi: Ch 4 |

| 8. | 13th August 2021 | Prime implicant chart and its reduction | Kohavi: Ch 4 |

| 9. | 16th August 2021 | Branching method, multi-output function minimization and Heuristic-based switching function minimization | Kohavi: Ch 4 |

| 10. | 20th August 2021 | Multi-level logic synthesis | Kohavi: Ch 6 |

| 11. | 23rd August 2021 | Multi-level logic Minimization - Algebraic Method | Kohavi: Ch 6 |

| 12. | 26th August 2021 | Multi-level logic Minimization - Algebraic Method | Kohavi: Ch 6 |

| 13. | 27th August 2021 | Combinational Logic Design (code conversion, parity generator, Comparator) | Kohavi: Ch 5, Mano: Ch 4 |

| 14. | 30th Aug 2021 | Combinational Logic Design (Multiplexer, Decoder) | Kohavi: Ch 5, Mano: Ch 4 |

| 15. | 2nd Sept 2021 | Combinational Logic Design (Encoder, Full Adder) | Kohavi: Ch 5, Mano: Ch 4 |

| 16. | 6th Sept 2021 | Combinational Logic Design (Ripple Carry Adder and Carry Look ahead adder) | Kohavi: Ch 5, Mano: Ch 4 |

| 17. | 9th Sept 2021 | Combinational Logic Design (BCD adder and Adder/subtractor Design, Overflow) | Mano: Ch 4 |

| 18. | 10th Sept 2021 | Combinational Logic Design (Multiplier, Implementation with NAND, NOR Gate) | Mano: Ch 4 |

| 19. | 13th Sept 2021 | CMOS Transistors and Gates | Kohavi: Ch 5 |

| 20. | 16th Sept 2021 | Introduction to digital circuits modeling using VERILOG | Palnitkar |

| 21. | 17th Sept 2021 | Introduction to digital circuits modeling using VERILOG | Palnitkar |

| 22-40 | Lectures taken by Dr. A. Sahu |

Examination Schedule (till Mid-Sem)

| Exam No | Date | Topic | Mode |

| 1 | 25th August | Lectures 1-9 | MCQ - Rapid Mode |

| 2 | 16th September | Lectures 10-18 | MCQ - Rapid Mode |

| 3 | 21st September | Lectures 1-21 | MCQ - Rapid Mode |