Chandan Karfa

CS 577: C-Based VLSI Design

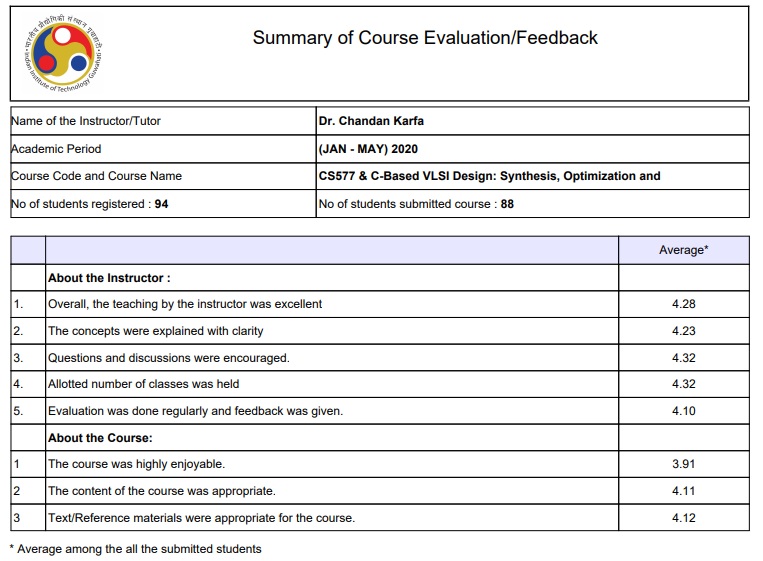

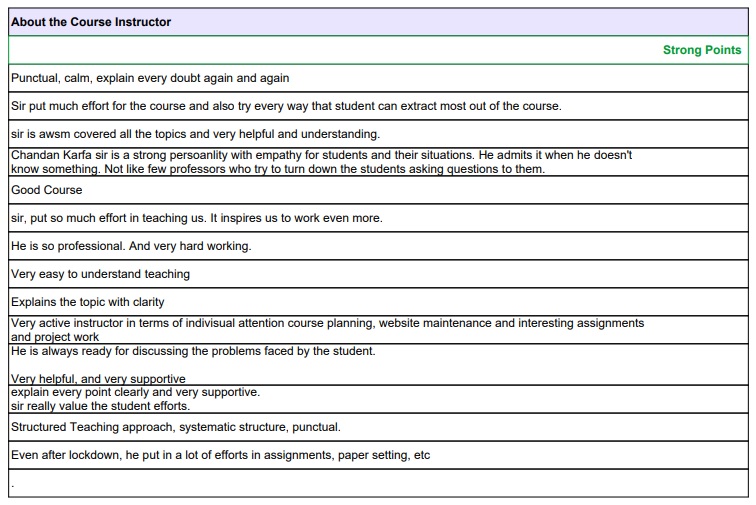

Course Feedback:

|

|

IMPORTANT UPDATE: Links to Video Lectures are given. Please check the Day-wise Schedule at the bottom of the page. Go through the lectures from home. I will schedule discussion sessions once you are back to campus. Feel free to send email if you have any doubts about any part of the lectures. I will clarify over email/phone/skype.

11th March 2020: Project Evaluation Schedule and Guidelines. Guidelines, Evaluation Scheme

14th February Guest Lecture by Prof. Ramesh Karri, New York University: Time: 6:30PM-7:30PM, Venue: CSE Seminar Room

VIVADO HLS Tool DOWNLOAD

Clas Test 1: 19th February 2020

No Class on 6th and 7th February 2020

Update your github id in the project page. One for each group. LINK

5th February 2020, Time: 6PM-7PMM. Venue: CSE Seminar Room. Topic: Project Discussion. There would be normal class as well.

30th January 2020, Time: 12PM-1pm, Venue: CSE Seminar room, Topic: HLS Tool Demo

[Project Allocation]: Make your group of four students. Fill the Google form group-wise by 21st January 2020. LINK

Welcome to CS 577 Course page

Cource Overview

High-level Synthesis (HLS) is the process of generating effecient hardware from C-code (high-level code). HLS is an active domain of research in recent times in the domain of electronic Design Automation (EDA) of VLSI. This course will help the student to (i) understand the overall HLS flow, (ii) how a C-code will be converted to its equivalent hardware, (iii) how to write C-code for efficient hardware generation and (iv) how the common software compiler optimization can help to improve the circuit performance. Also, advanced topics like HLS for security, optimizations at RTL level and verification challenges of HLS will be covered. The overall EDA tool flow will also be covered briefly. This course will help the students to take up research in the domain of HLS. Also, this course will help the students to become proficient for EDA industries.

Pre-requisites: (1) Basic knowledge of digital circuits (2) Basic knowledge of Data structures and algorithms

Instructors

Dr. Chandan Karfa

Class Timing and Venue:

Wednesday: 12PM-1PM, Thursday: 12PM-1PM, Friday: 12PM-1PM

Venue: 3202

TAs with their Responsibilities:

Priyanka Panigrahi - priya176101006@iitg.ac.in - Evaluation of Quizzes

Ramanuj Chouksey - r.chouksey@iitg.ac.in – Mentor for Verification related Projects

Debabrata Senapati - debab176101003@iitg.ac.in – Scribe management

Modammed Abderahman - ma.adem@iitg.ac.in – Mentor for HLS related projects

Oza Jay - oza@iitg.ac.in – Mentor for HLS related projects

Yom Nigam - yom@iitg.ac.in – Mentor for HLS related projects

Syllabus:

Electronic Design Automation flow: Overview of high-level synthesis, logic synthesis and physical synthesis;

High-level Synthesis (HLS) Fundamentals: Overview HLS flow, Scheduling Techniques, Resource sharing and Binding Techniques, Datapath and Controller Generation Techniques;

Impact of C-coding style on Hardware: Data types, Synthesis of Loops, Functions, RAM, ROM, Shift register inference from arrays;

Impact of Compiler Optimization in HLS results: Impact of Compiler optimizations like copy propagation, constant propagation, common sub-expression elimination, loop transformations, code motions, etc., in HLS results;

HLS for Security: RTL Locking, Logic Locking, Attack and Defense techniques;

RTL Optimizations Techniques: Various optimization techniques to improve latency, area and power in C-based VLSI designs;

High-level Synthesis Verification: BDD, Simulation based verification, Equivalence checking between C and RTL;

Text Book:

[Micheli] G. De Micheli. Synthesis and optimization of digital circuits, McGraw Hill, India Edition, 2003.

[Elliot] J. P. Elliot, Understanding Behavioural Synthesis: A Practical guide to High-level Synthesis, Springer, 2nd edition, 2000

[Kilts] Steve Kilts, Advanced FPGA Design, Wiley, 2007.

[Parhi] K. Parhi: VLSI Digital Signal Processing Systems: Design and Implementation, Jan 1999, Wiley.

[Huth] M. Huth and M. Ryan, Logic in Computer Science: Modelling and Reasoning about Systems, 2nd Ed, Cambridge University Press, 2004.

Various Research Papers.

References:

[Gajski] D. D. Gajski, N. D. Dutt, A.C.-H. Wu and S.Y.-L. Lin, High-Level Synthesis: Introduction to Chip and System Design, Springer, 1st edition, 1992

[BlueBook] Mike Fingeroff, High-Level Synthesis Blue Book, Mentor Graphics Corporation, 2010.

Philippe Coussy and Adam Morawiec, High-level Synthesis from Algorithm to Digital Circuit, Springer, 2008

David. C. Ku and G. De Micheli, High-level Syntehsis of ASICs Under Timing and Synchronization Constraints, Kluwer Academic Publishers, 1992.

T. F. Melham, Higher Order Logic and Hardware Verification, Cambridge University Press, 1993.

Grade Calculation

| Quizzes + Scribe/Class Participation | 20% |

| Projects/Research Studies | 20% |

| MidSem | 20% |

| End Sem | 40% |

Classes

| Sl No | Date | Topic | Resources |

| 1 | 3rd Jan 2020 | Course Overview, Introduction to EDA Flow | Scribe |

| 2 | 8th Jan 2020 | HLS flow with an example | Scribe |

| 3. | 9th Jan 2020 | HLS flow with an example | Scribe |

| 4. | 10th Jan 2020 | HLS Steps | Scribe |

| 5. | 16th Jan 2020 | Scheduling Problem formulations, ASAP, ALAP | Micheli: Ch 5, Scribe |

| 6. | 17th Jan 2020 | ILP formulation of ML-RC and MR-LC | Micheli: Ch 5, Scribe |

| 7. | 20th Jan 2020 | Multiprocessor Scheduling, Lower bound of resource | Micheli: Ch 5, Scribe |

| 8. | 22th Jan 2020 | HUs’ algorithm, List Scheduling | Micheli: Ch 5, Scribe |

| 9. | 23rd Jan 2020 | List Scheduling for ML_RC and MR_LC | Micheli: Ch 5, Scribe |

| 10. | 24th Jan 2020 | Path Based Scheduling | Scribe, Paper |

| 11. | 29th Jan 2020 | Path Based Scheduling | Scribe |

| 12. | 30th Jan 2020 | HLS Tool Demo | Resource |

| 13. | 5th Feb 2020 | Resource Allocation and Binding | Micheli: Ch 6, Scribe |

| 14. | 5th Feb 2020 | Guest Lecture by Deepraj Soni, NYU | Slides |

| 15. | 12th Feb 2020 | Resource Allocation and Binding | Micheli: Ch 6, Scribe |

| 16. | 13th Feb 2020 | Verilog Basic | Slides |

| 17. | 14th Feb 2020 | Resource Allocation and Binding | Scribe |

| 18. | 14th Feb 2020 | HLS for Security by Prof. Ramesh Karri, NYU | Paper |

| 19. | 19th Feb 2020 | Class Test 1 | |

| 20. | 20th Feb 2020 | HLS of Arrays | Manual, Scribe |

| 21. | 25th Feb 2020 | HLS of Loops | Scribe |

| 4th March 2020 | Mid-Semester Examination | ||

| 22. | 5th March 2020 | HLS of Loops | Scribe |

| 23. | 6th March 2020 | Compiler Optimization for HLS | Scribe |

| 24. | 11th March 2020 | Retiming | |

| 25. | 13th March 2020 | Retiming | Video Lecture (YouTube) |

| 26. | 18th March 2020 | RTL Optimizations for Timing | Video Lecture (YouTube) |

| 27. | 19th March 2020 | RTL Optimizations for Area | Video Lecture (YouTube) |

| 28. | 20th March 2020 | RTL Optimizations for Power | Video Lecture (YouTube) |

| 29. | 25th March 2020 | Introduction to Logic Synthesis | Video Lecture (YouTube) |

| 30. | 26th March 2020 | Introduction to FPGA Mapping | Video Lecture (YouTube) |

| 31. | 27th March 2020 | Introduction to Physical Synthesis | Video Lecture (YouTube) |

| 32. | 1st April 2020 | Verification: LTL-CTL Based Verification | Video Lecture (YouTube) |

| 33. | 2nd April 2020 | Verification of Large Systems | Video Lecture (YouTube) |

| 34. | 3rd April 2020 | BDD Based Verification | Video Lecture (YouTube) |

| 35. | 8th April 2020 | ADD, HDD Based Verification | Video Lecture (YouTube) |

| 36. | 9th April 2020 | Symbolic Model Checking | Video Lecture (YouTube) |

| 37. | 16th April 2020 | Bounded Model Checking | Video Lecture (YouTube) |