Chandan Karfa

CS 577: C-Based VLSI Design: Synthesis, Optimization and Verification

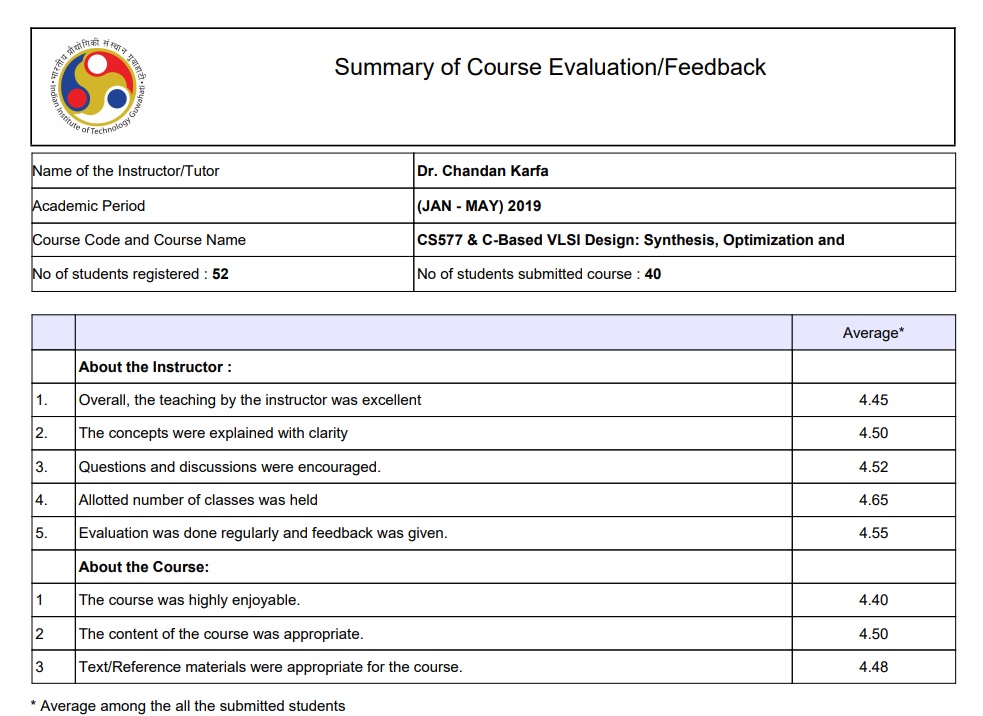

Course Feedback:

|

|

Grades: Total Registered Students: 52. AS: 1, AA: 6, AB: 10, BB: 6, BC: 11, CC: 8, CD: 5, DD: 4, FP: 2.

End-Sem Paper Clarification: 9th May 2019: 5PM-7PM, CSE Seminar Room.

Venue Change: The class on 2nd April will be held in CSE Seminar Room from 11AM to 12:30PM.

Project Review: LeFlow, 3rd April, CSE Seminar Room from 5:30PM to 6:30PM.

Class Test 2 will be held on 5th April 2019

No Class on 1st April 2019 and 16th April 2019

Presentation Schedule: Projects: Phase 1: 18th March 2019 (Monday), 6PM-7PM, CSE Seminar Room. Phase 2: 24th April 2019 (Wednesday), 5:30PM-7PM, CSE Seminar Room. Paper Presentation: Phase 1: 20th March 2019 (Wednesday), 5PM-7PM, CSE Conference Room. Phase 2: 25th April 2019 (Thursday), 5:30PM-7PM, CSE Conference Room.

Guest Lecture RESCHEDULED:* by Prof. Ramesh Karri on ‘‘High-Level Synthesis for Security’’. Schedule: 8AM-9AM, 20th February 2019, Venue: CSE Seminar Room.

HLS Tool Demo: Wednesday (7th February 2019), 6PM-7PM, CSE Seminar Room

No Class on Friday (8th February 2019 and 11th February 2019). I will be out of station.

Class Test 1: Monday (18th Feb 2019) 10AM-11AM, Syllabus: topic taught till 5th February 2019.

Guest Lecture by Prof. Ramesh Karri on ‘‘High-Level Synthesis for Security’’. Schedule: 8AM-9AM, 13th February 2019, Venue: CSE Seminar Room.

Guest Lecture by Dr. Sukanta Bhattacharjee on ‘‘Overview of microfluidic sample preparation and few related algorithms’’. Schedule: 11AM-12PM, 12th February, 2019, Venue: CSE Seminar Room.

The class of 25th January (Friday) is rescheduled to 30th January 2019 during 6PM-7PM in CSE Seminar Room.

No class on 25th January (Friday). Next class is on 28th January 2019 (Monday).

[Project and RS Allocation]: Fill the Google form group-wise by 26th January 2019. A group will consist maximum of three students. LINK

Cource Overview

High-level Synthesis (HLS) is the process of generating effecient hardware from C-code (high-level code). HLS is an active domain of research in recent times in the domain of electronic Design Automation (EDA) of VLSI. This course will help the student to (i) understand the overall HLS flow, (ii) how a C-code will be converted to its equivalent hardware, (iii) how to write c-code for efficient hardware generation and (iv) how the common software compiler optimization can help to improve the circuit performance. Also, advanced topics like Relative Scheduling, IO scheduling modes, handshaking and HLS for FPGA targets, optimizations at RTL level and verification challenges of HLS will be covered. This course will help the students to take up research in the domain of HLS. Also, this course will help the student to become proficient for EDA industries.

Pre-requisites: (1) Basic knowledge of digital circuits (2) Basic knowledge of Data structures and algorithms

Instructors

Dr. Chandan Karfa

Class Timing and Venue:

Friday: 9AM-9:55AM, Monday: 10AM-10:55AM, Tuesday: 11AM-11:55AM

Venue: 3102

Syllabus:

Electronic Design Automation flow: Overview of high-level synthesis, logic synthesis and physical synthesis;

High-level Synthesis (HLS) Fundamentals: Overview HLS flow, Scheduling Techniques, Resource sharing and Binding Techniques, Data-path and Controller Generation Techniques;

Impact of C-coding style on Hardware: Data types, Synthesis of Loops, Functions, RAM, ROM, Shift register inference from arrays;

Impact of Compiler Optimization in HLS results: Impact of Compiler optimizations like copy propagation, constant propagation, common sub-expression elimination, loop transformations, code motions, etc., in HLS results;

Secure HLS, Relative Scheduling, IO scheduling modes, Pipelining, Handshaking, System Design, High-Level Synthesis for FPGA;

RTL Optimizations Techniques: Various optimization techniques to improve latency, area and power in C-based VLSI designs;

High-level Synthesis Verification: Simulation based verification, Translation validation. Equivalence checking between C and RTL;

Text Book:

[Micheli] G. De Micheli. Synthesis and optimization of digital circuits, McGraw Hill, India Edition, 2003.

[Elliot] J. P. Elliot, Understanding Behavioural Synthesis: A Practical guide to High-level Synthesis, Springer, 2nd edition, 2000

[Kilts] Steve Kilts, Advanced FPGA Design, Wiley, 2007.

[Parhi] K. Parhi: VLSI Digital Signal Processing Systems: Design and Implementation, Jan 1999, Wiley.

[Huth] M. Huth and M. Ryan, Logic in Computer Science: Modelling and Reasoning about Systems, 2nd Ed, Cambridge University Press, 2004.

References:

[Gajski] D. D. Gajski, N. D. Dutt, A.C.-H. Wu and S.Y.-L. Lin, High-Level Synthesis: Introduction to Chip and System Design, Springer, 1st edition, 1992

[BlueBook] Mike Fingeroff, High-Level Synthesis Blue Book, Mentor Graphics Corporation, 2010.

Philippe Coussy and Adam Morawiec, High-level Synthesis from Algorithm to Digital Circuit, Springer, 2008

David. C. Ku and G. De Micheli, High-level Syntehsis of ASICs Under Timing and Synchronization Constraints, Kluwer Academic Publishers, 1992.

T. F. Melham, Higher Order Logic and Hardware Verification, Cambridge University Press, 1993.

TAs:

Priyanka Panigrahi (priya176101006@iitg.ac.in))

Rajesh Kumar Jha (rajes174101007@iitg.ac.in)

Grade Calculation

| Quizzes | 15% |

| Projects | 10% |

| Scribe | 5% |

| MidSem | 30% |

| End Sem | 40% |

Classes

| Sl No | Date | Topic | Resources |

| 1 | 4th Jan 2019 | Introduction to VLSI automation flow | Class Note by Priyanka |

| 2 | 7th Jan 2019 | Introduction to C-Based VLSI Design /High-level Synthesis (HLS) | Class Note by Kunal and Shavi, Class Note by Amit and Thathagata |

| 3 | 8th Jan 2019 | Class suspended | |

| 4 | 11th Jan 2019 | HLS flow with an example | Class Note by Amit and Thathagata |

| 5 | 18th Jan 2019 | HLS flow with an example (continue) | Class Note by Deekshit |

| 6 | 21st Jan 2019 | Scheduling Problems formulation, ASAP, ALAP | Mitcheli: Ch 5, Class Note by Abhisekh |

| 7 | 22nd Jan 2019 | ILP formulations of ML-RC Scheduling | Mitcheli: Ch 5, Class Note by Chiranjeevi |

| 25th Jan 2019 | No Class. Rescheduled | ||

| 8 | 28th Jan 2019 | ILP of MR-LC Scheduling, Multiprocessor Scheduling: HU's algo | Mitcheli: Ch 5, Class Note by Mayank |

| 9 | 29th Jan 2019 | List Scheduling ML-RC and MR-LC formulation | Mitcheli: Ch 5, Class Note by Monika |

| 10 | 31st Jan 2019 | Synthesis for control dominated C-code | Class Note by Gouri Sankar |

| 11 | 4th Feb 2019 | Path-based Scheduling | Paper, Class Note by Gouri Sankar |

| 12 | 5th Feb 2019 | Scheduling under timing constraints | Mitcheli: Ch 5, Mitcheli: Ch 2.4, Class Note by Karnish |

| 13 | 6th Feb 2019 | HLS Tools Demo | Book1, Book2, Vivado Slide, Vivado Flow, LeFlow Slide, Vivado Link, LeFlow Paper |

| 14 | 12th Feb 2019 | Guest Lecture by Dr. Sukanta Bhattacharjee | Slides, Book, Paper1, Paper2, Paper3 |

| 15 | 15th Feb 2019 | Allocation and binding: Problem Formulation | Micheli: Ch 6 |

| 16 | 16th Feb 2019 | FU allocation and binding for non-hierarchical graph | Micheli: Ch 6, Class Note by Kavitha |

| 17 | 18th Feb 2019 | Class Test 1 | |

| 18 | 19th Feb 2019 | ILP formulation, FU alloc and bind for hierarchical graph | Micheli: Ch 6, Class Note by Krishna Praveen |

| 19 | 20th Feb 2019 | Guest Lecture by Prof. Ramesh Karri | Slides |

| 20 | 22nd Feb 2019 | Register allocation and binding, Port assignment problem | Micheli: Ch 6, Class Note by Shiva |

| 27th Feb 2019 | Mid-Semester Examination | ||

| 21 | 11th March 2019 | Compiler Optimizations and its impact in HLS | Micheli: Ch 3.4, Class Note by Sumita |

| 22 | 12th March 2019 | Compiler Optimizations and its impact in HLS (contd.) | Micheli: Ch 3.4, Class Note by Sujit |

| 18th March 2019 | Project Review | ||

| 23 | 18th March 2019 | HLS of Loops | BlueBook: Class Note by Saurabh |

| 24 | 19th March 2019 | HLS of Loops | Class Note by Kushal |

| 19th March 2019 | Project Review | ||

| 25 | 22nd March 2019 | C-Coding Style for HLS | Class Note by Abhisekh |

| 26 | 23rd March 2019 | C-Coding Style for HLS | Class Note by Sushant |

| 27 | 25th March 2019 | C-Coding Style for HLS | Class Note by Shubham |

| 28 | 26th March 2019 | RTL Optimizations: Retiming | Parhi: Ch 4, Class Note by Megha |

| 29 | 29th March 2019 | RTL Optimizations: Retiming | Parhi: Ch 4, Class Note by Ayasha |

| 30 | 2nd April 2019 | HLS for Reliability by Dr. Arnab Sarkar | Slides |

| 31 | 5th April 2019 | Class Test 2 | |

| 32 | 8th April 2019 | RTL Optimizations | Slide1, Class Note by Sunil |

| 33 | 9th April 2019 | RTL Optimizations | Slide, Slide2 |

| 34 | 12th April 2019 | FPGA Technology Mapping | Slides |

| 35 | 22nd April 2019 | FPGA Technology Mapping | Paper |

| 24th April 2019 | Project Review | ||

| 25th April 2019 | Project Review | ||

| 36 | 26th April 2019 | BDD | Micheli: 2.5, Class Note by Dharmendra |

| 37 | 27th April 2019 | BDD | Mitcheli: 2.5 Class Note by Rajat |

| 38 | 29th April 2019 | HLS Verification | Paper, Class Note by Ashwin |

| 39 | 30th April 2019 | HLS Verification | Paper, Class Note by Abhisekh and Ankit |

| 40 | 3rd May 2019 | HLS Verification | Paper |

| 8th May 2019 | End-Semester Examination |